#### Persistency Semantics of the Intel-x86 Architecture

Azalea Raad<sup>1,2</sup> John Wickerson<sup>2</sup> Gil Neiger<sup>3</sup> Viktor Vafeiadis<sup>1</sup>

<sup>1</sup> Max Planck Institute for Software Systems (MPI-SWS) <sup>2</sup> Imperial College London <sup>3</sup> Intel Corporation

## Computer Storage

✓ fastX volatile

X slow √ persistent

# What is Non-Volatile Memory (NVM)?

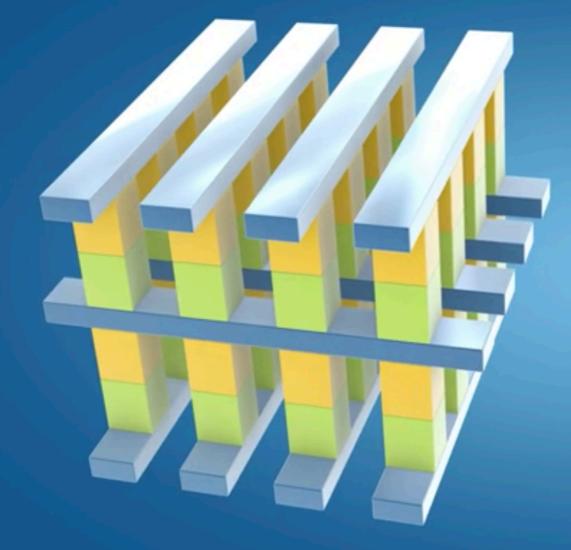

#### NVM: Hybrid Storage + Memory

Best of both worlds:

- ✓ *persistent* (like HDD)

- √ fast, random access (like RAM)

# INTEL® OPTANETM TECHNOLOGY

## **Q**: Why *Formal* NVM Semantics?

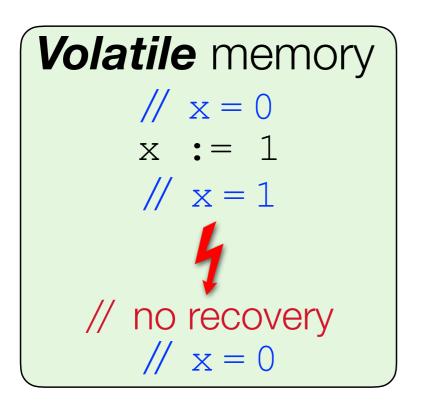

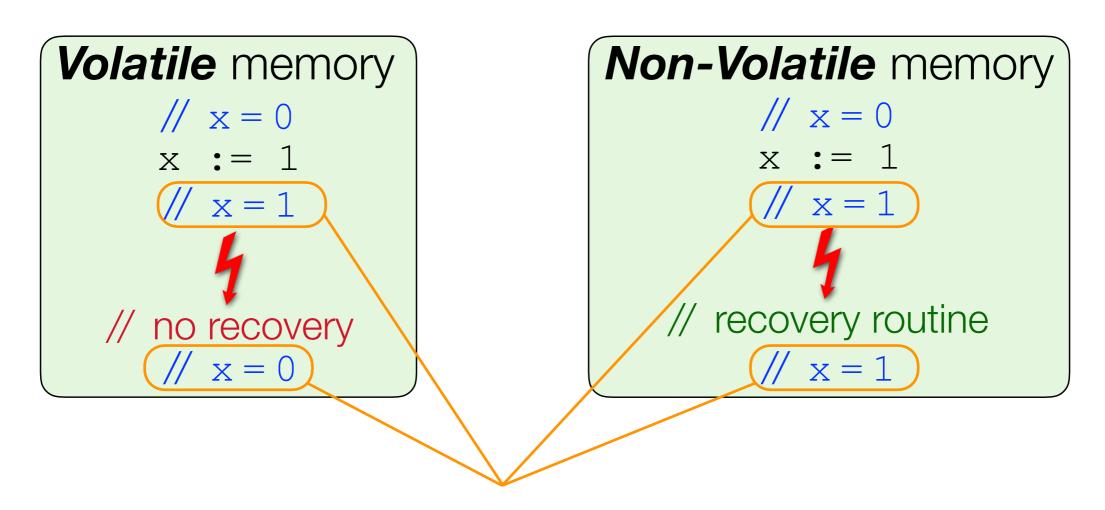

Non-Volatile memory // x = 0 x := 1 // x = 1 // x = 1 // recovery routine // x = 1

# **Q**: Why *Formal* NVM Semantics?

## A: Program Verification

## **Q**: Why *Formal* NVM Semantics?

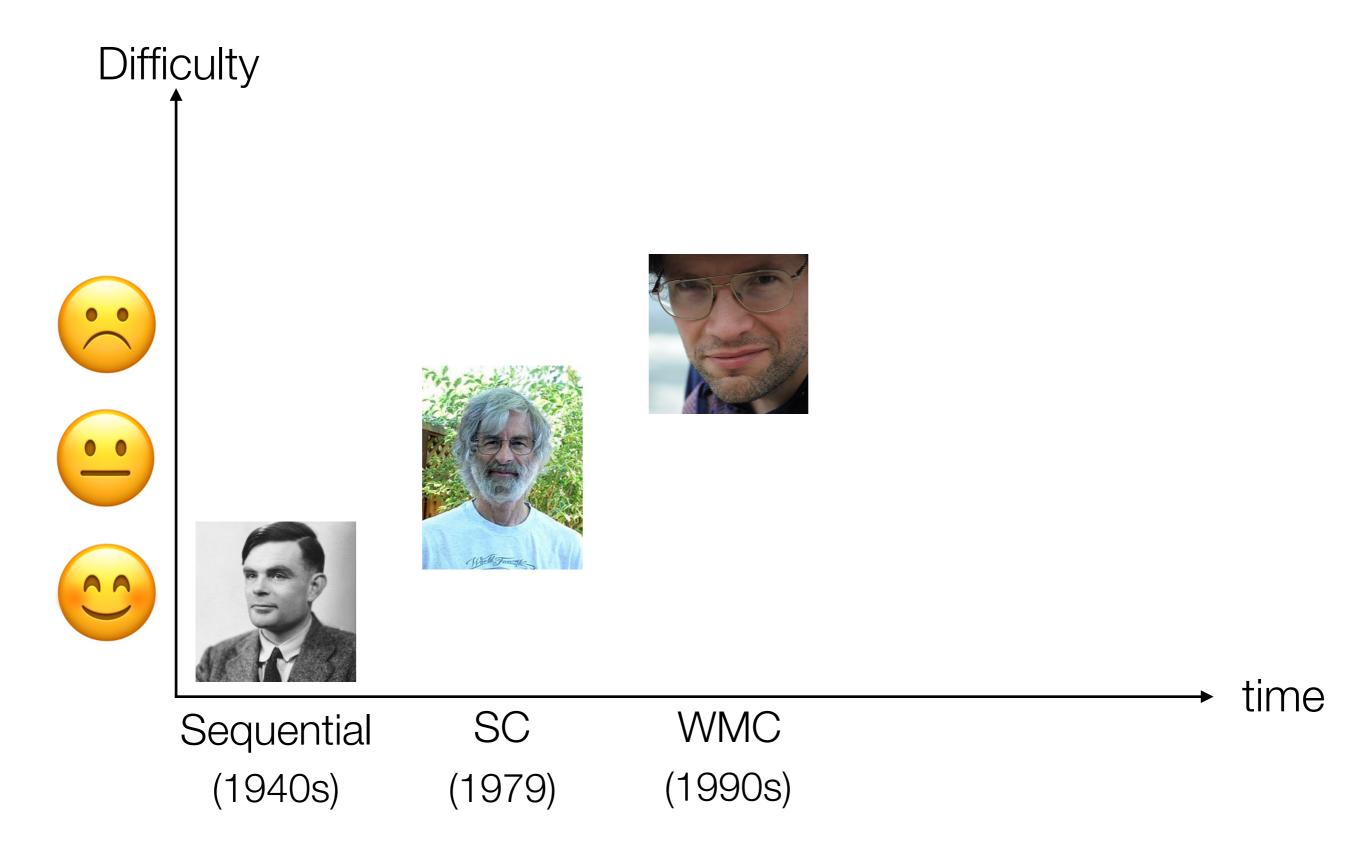

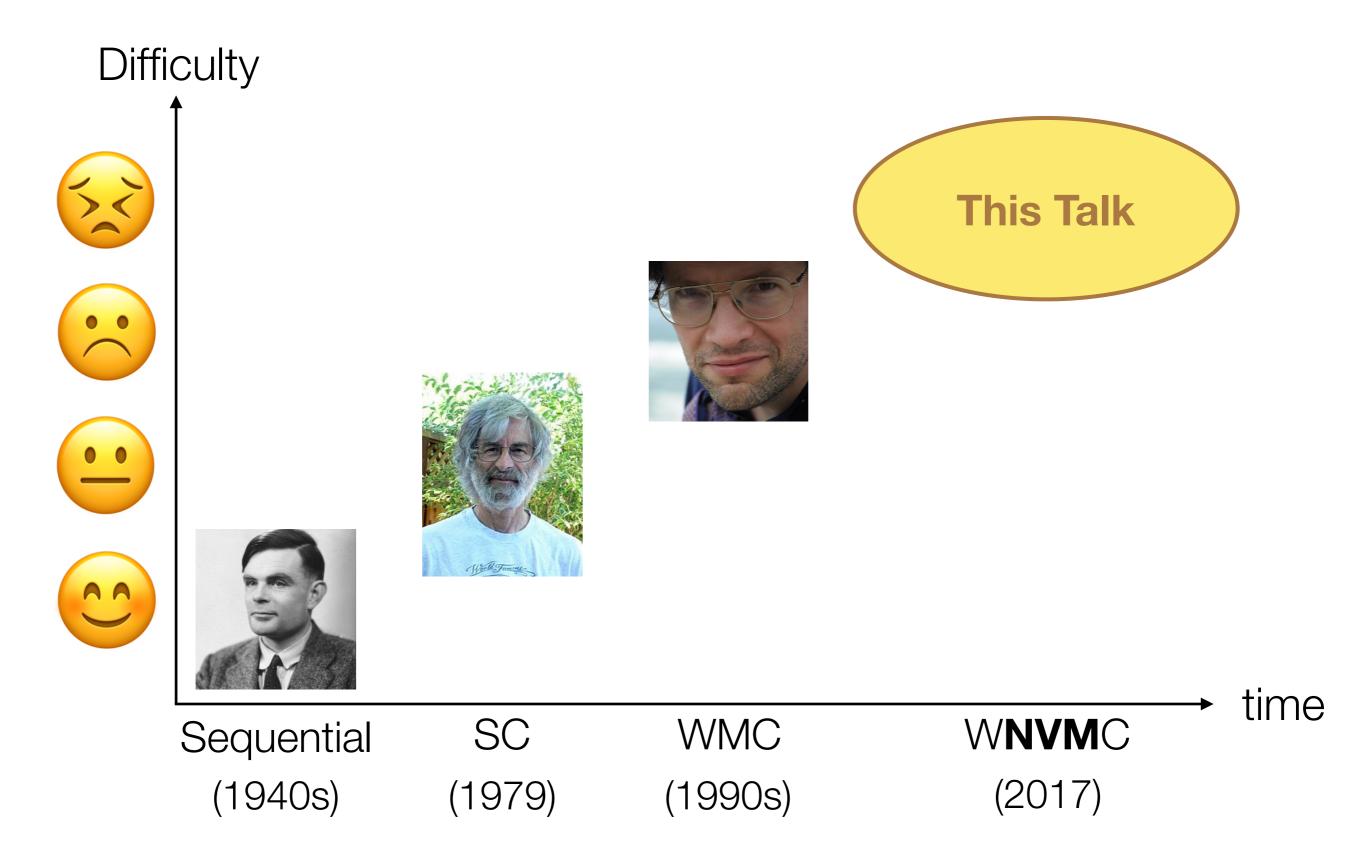

#### Formal Semantic Models

## Weak Memory Consistency (WMC)

**No** total execution order (*to*)  $\Rightarrow$

weak behaviour absent under SC, caused by:

- instruction *reordering* by compiler

- write propagation across *cache hierarchy*

## Weak Memory Consistency (WMC)

**No** total execution order (*to*)  $\Rightarrow$

- instru

- write

#### **Consistency Model**

the **order** in which writes are made visible to other threads

e.g. x86 (TSO), ARMv8, C11, Java

#### Formal Semantic Models

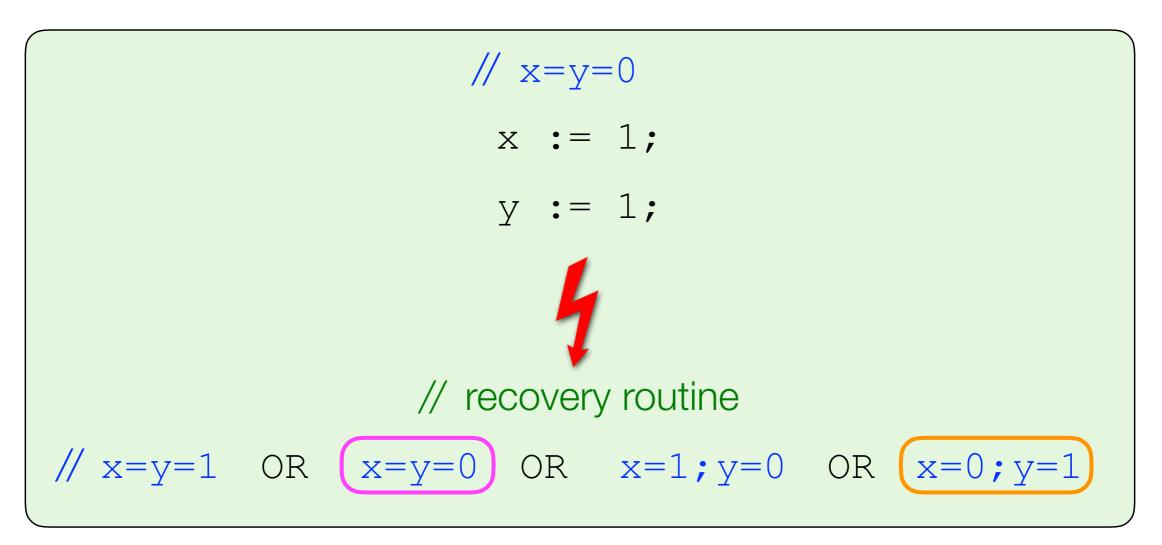

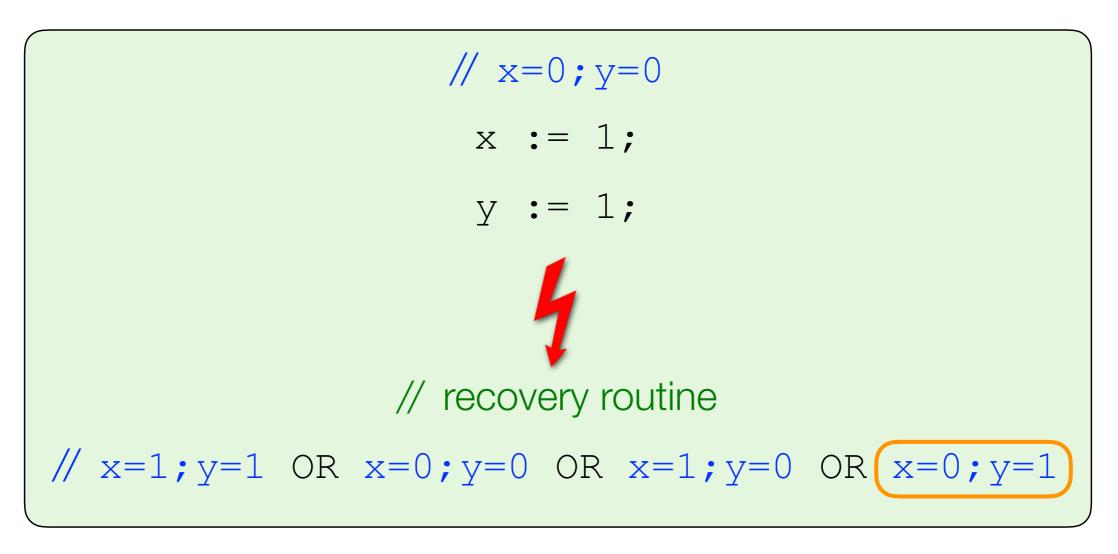

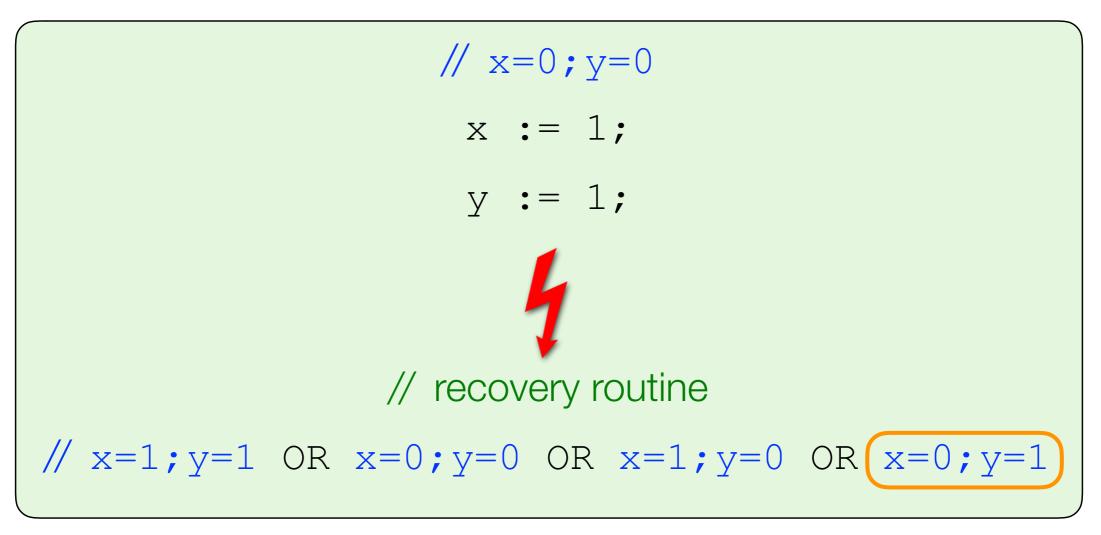

## What Can Go Wrong?

- I Execution continues ahead of persistence — asynchronous persists

- !! Writes may persist out of order

- *relaxed* persists

# What Can Go Wrong?

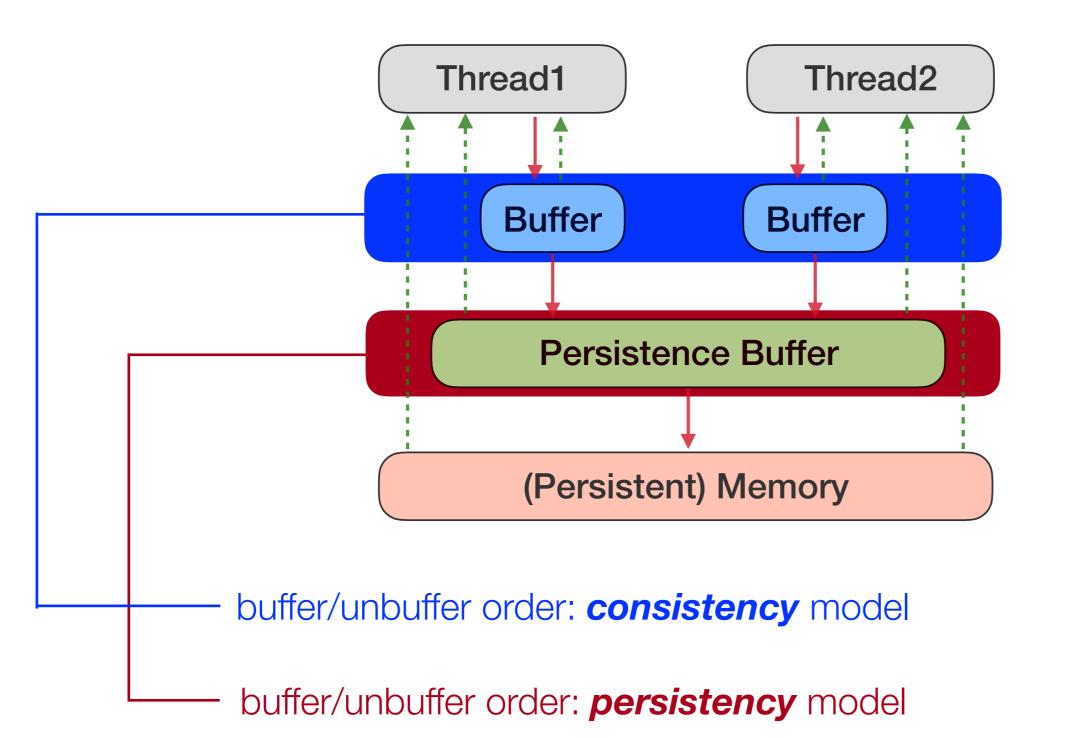

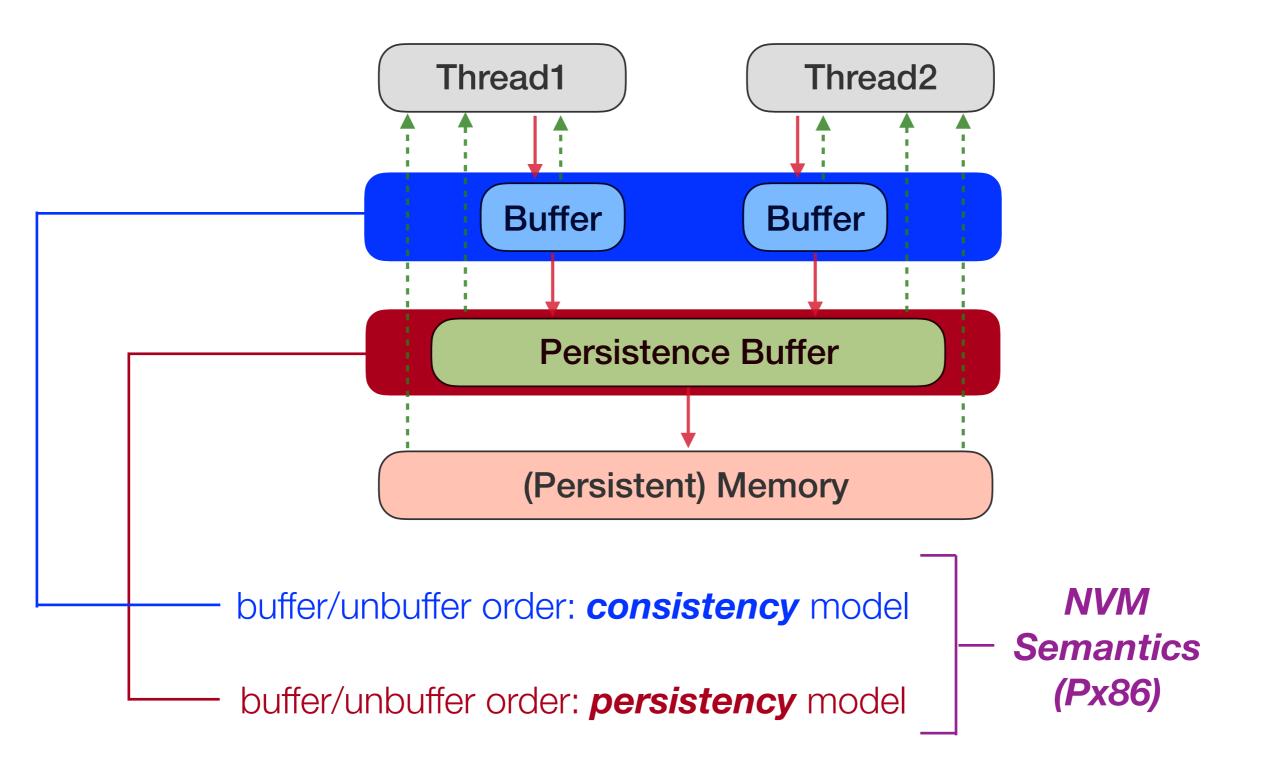

#### **Consistency Model**

the *order* in which writes are *made visible* to other threads

#### **Persistency Model**

the **order** in which writes are **persisted** to NVM

// x=

!! F

#### **NVM Semantics** Consistency + Persistency Model

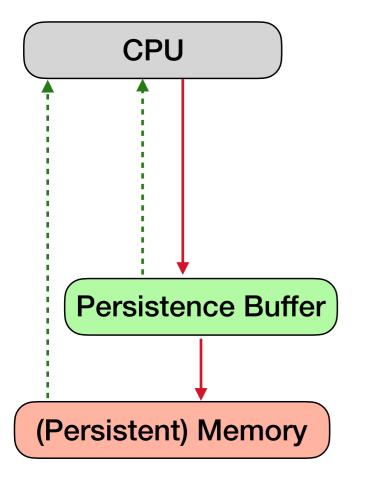

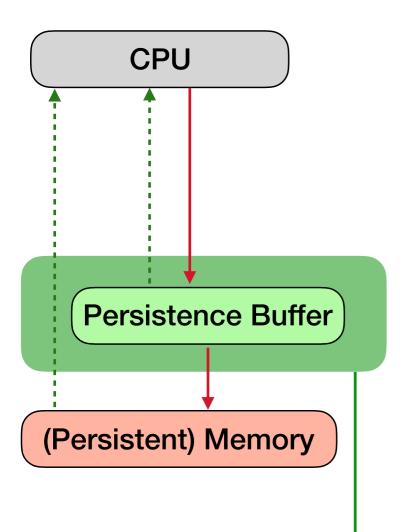

# Warmup: **Sequential** Px86

x := 1 : adds x := 1 to p-buffer

x := 1 : adds x := 1 to p-buffer

unbuffer\* : p-buffer to memory

Unbuffered at *non-deterministic* points in time!

x := 1 : adds x := 1 to p-buffer

unbuffer\* : p-buffer to memory

Unbuffered at *non-deterministic* points in time!

Buffering & unbuffering orders may disagree!

<sup>\*</sup> at non-deterministic times

x := 1 : adds x := 1 to p-buffer

unbuffer\* : p-buffer to memory

a:=x : if p-buffer contains x, reads latest entry else reads from memory

Unbuffered at *non-deterministic* points in time!

Buffering & unbuffering orders may disagree!

<sup>\*</sup> at non-deterministic times

x := 1 : adds x := 1 to p-buffer

unbuffer\* : p-buffer to memory

a:=x : if p-buffer contains x, reads latest entry else reads from memory

p-buffer lost; memory retained

Unbuffered at *non-deterministic* points in time!

Buffering & unbuffering orders may disagree!

<sup>\*</sup> at non-deterministic times

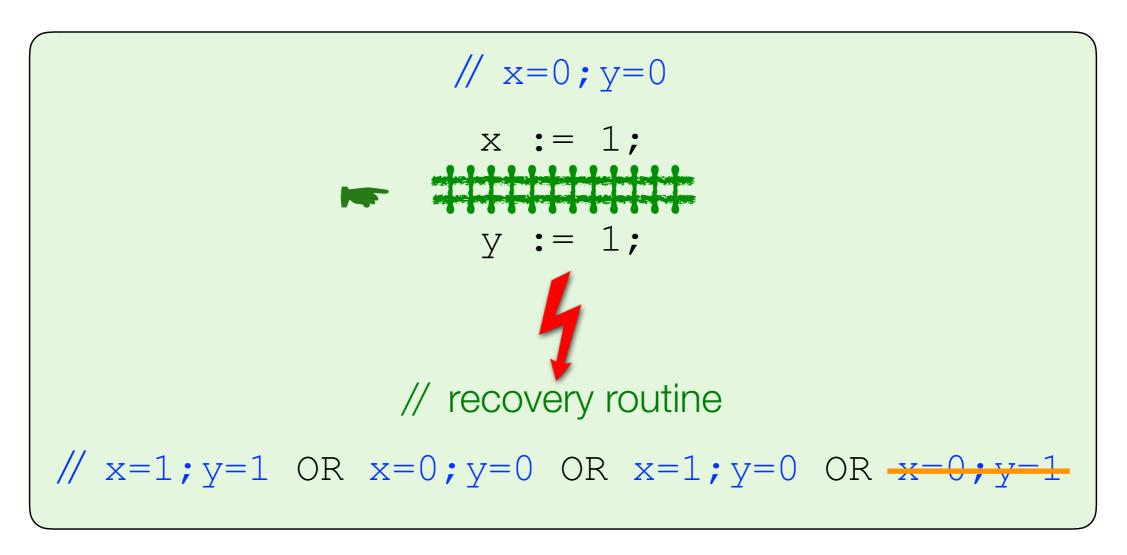

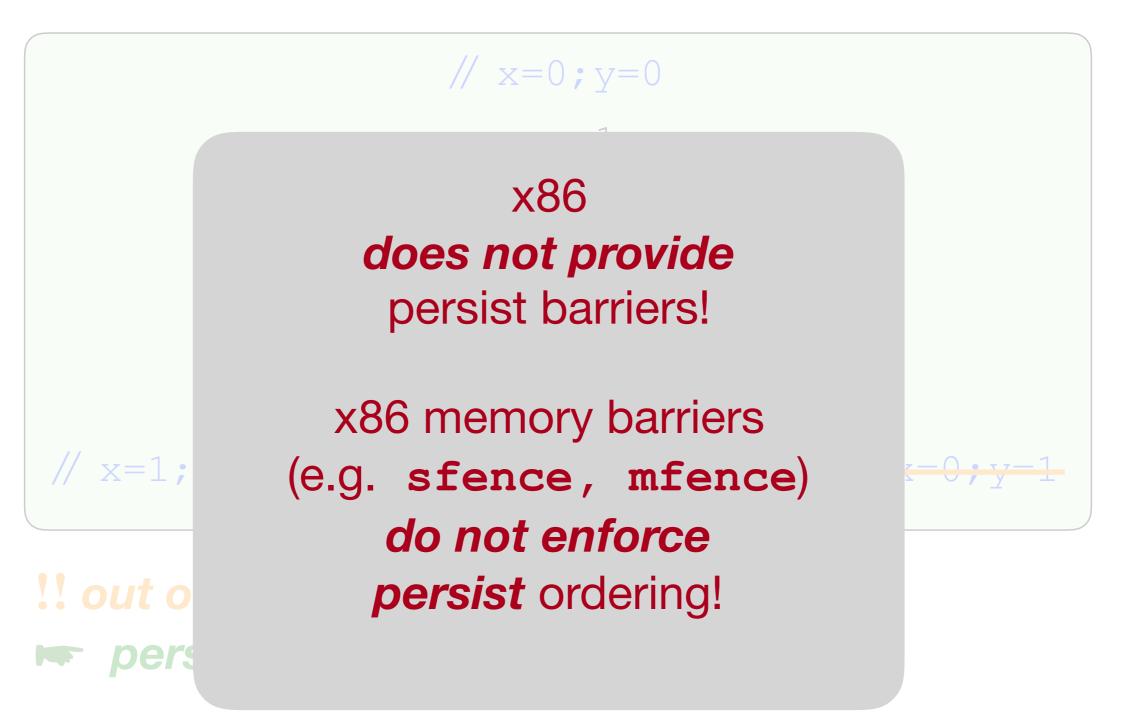

## Fixing Relaxed Persists: Attempt #1

!! out of order persists

persist barriers?

#### Persist Barriers: Desiderata

!! out of order persists

persist barriers?

#### Persist Barriers: Desiderata

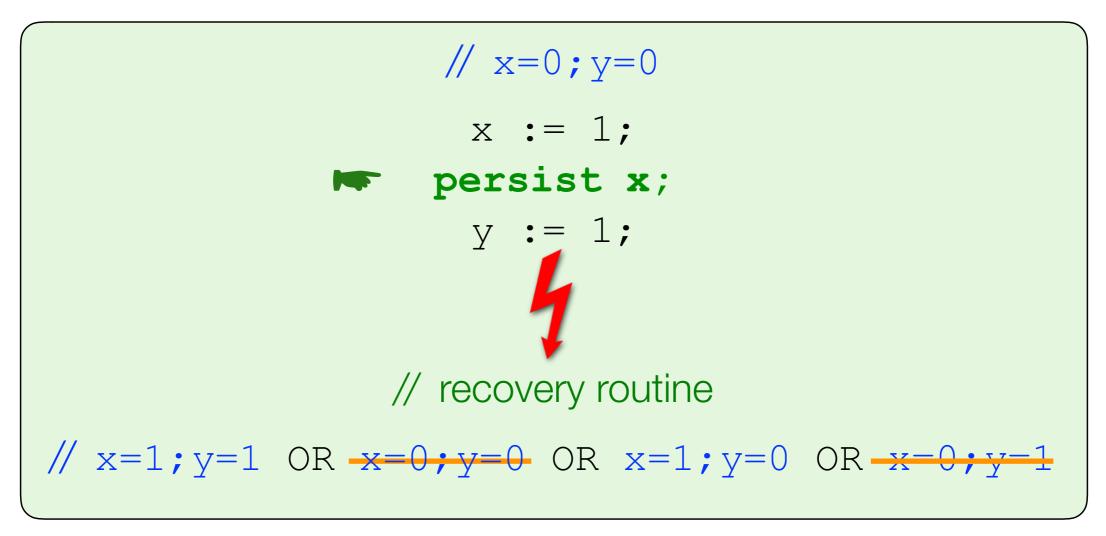

## Fixing **Relaxed** Persists: Attempt #2

**!! out of order persists**

explicit persists?

#### Explicit Persists: Desiderata

**!! out of order persists**

explicit persists?

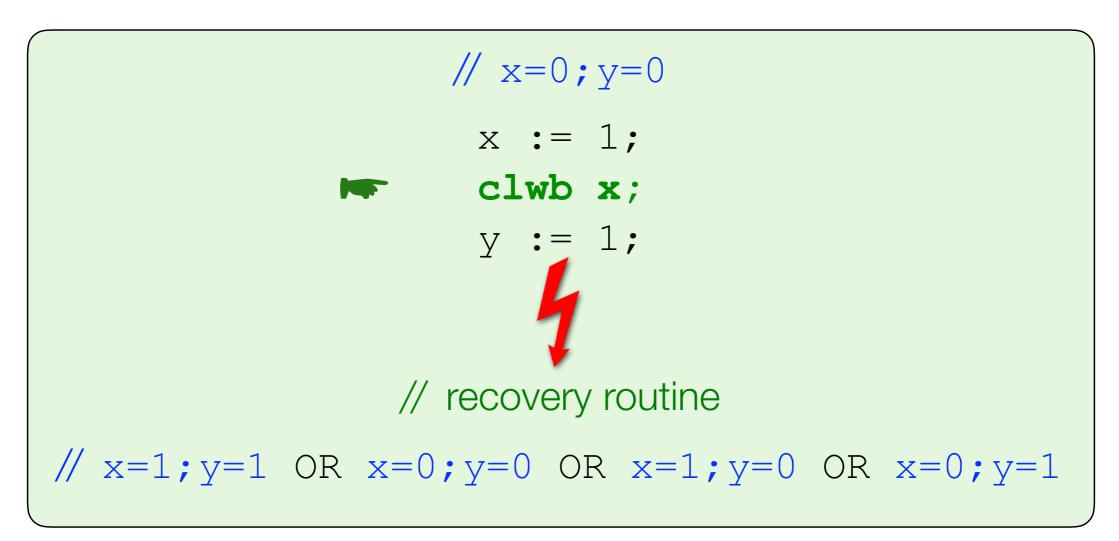

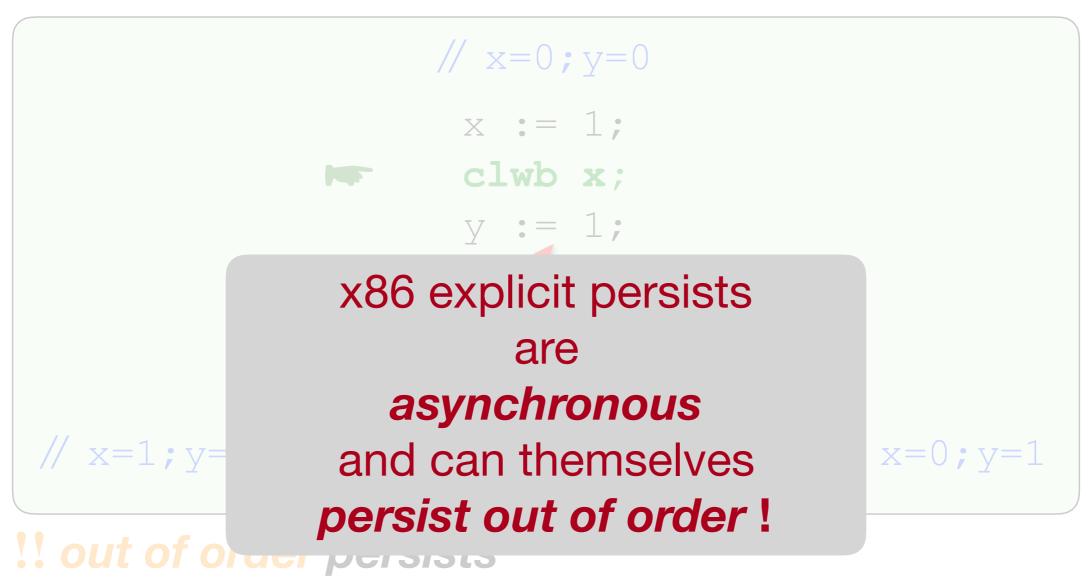

## Explicit Persists: Reality on x86

#### **!! out of order persists**

explicit persists?

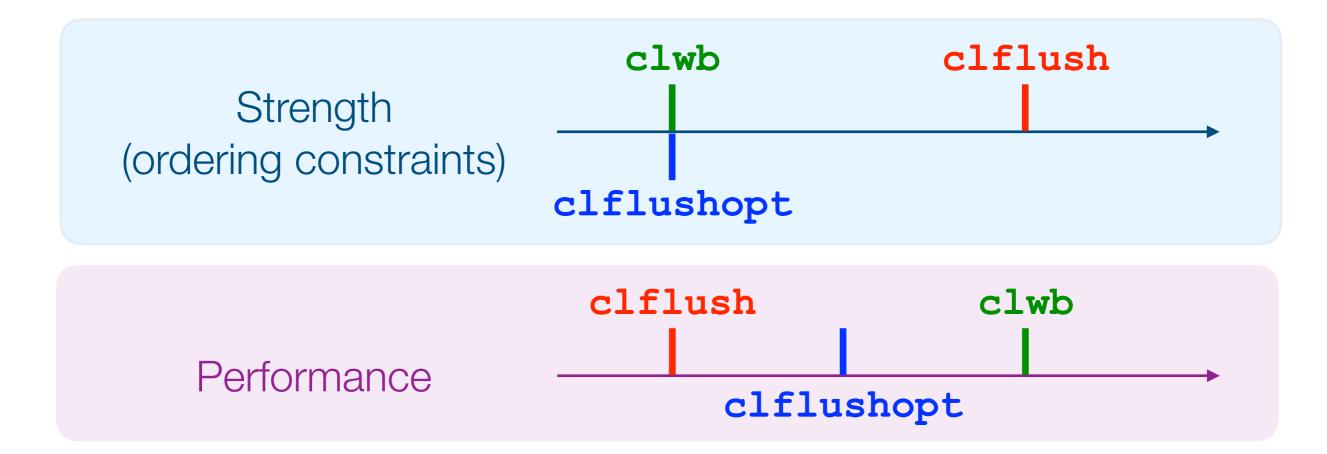

clwb x/clflushopt x/clflush x:

asynchronously persist cache line containing x

## Explicit Persists: Reality on x86

explicit persists?

clwb x/clflushopt x/clflush x:

asynchronously persist cache line containing x

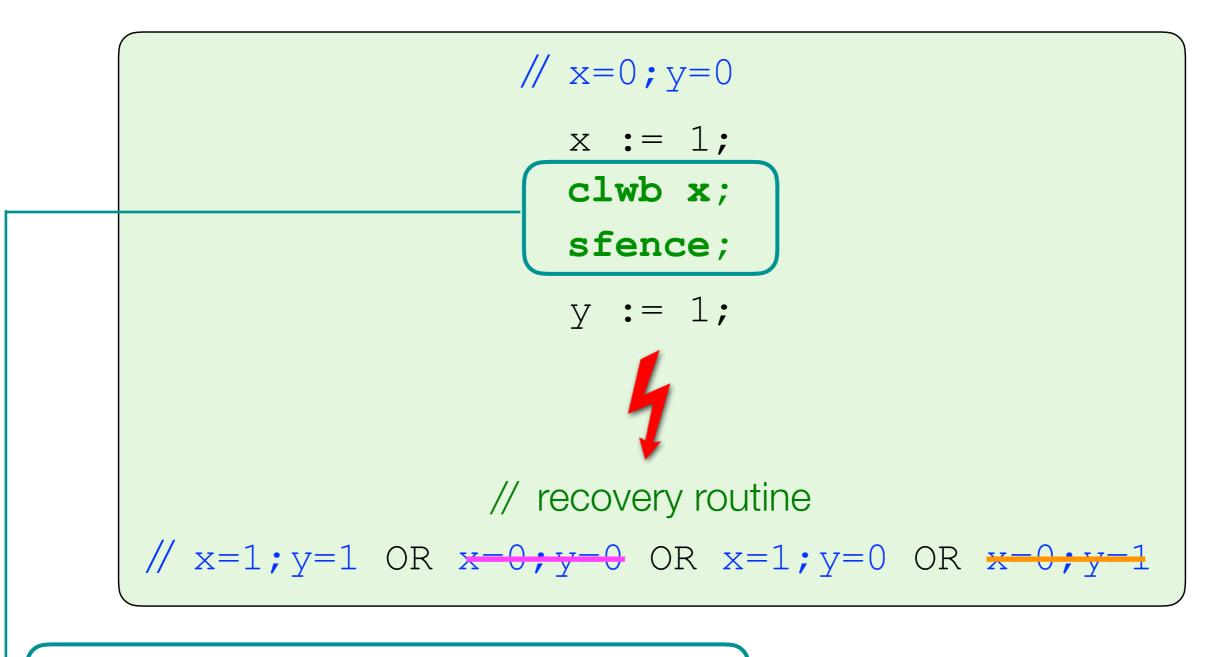

## Solution: Persist Sequence

Waits until earlier writes on x are persisted

Disallows reordering

✓ synchronous persists

✓ no out of order persists

#### x86 Persists: clwb, clflushopt, clflush

- \* clwb and clflushopt: same ordering constraints

- \* clwb does not invalidate cache line

- \* clflushopt invalidates cache line

- Clflush: strongest ordering constraints; invalidates cache line

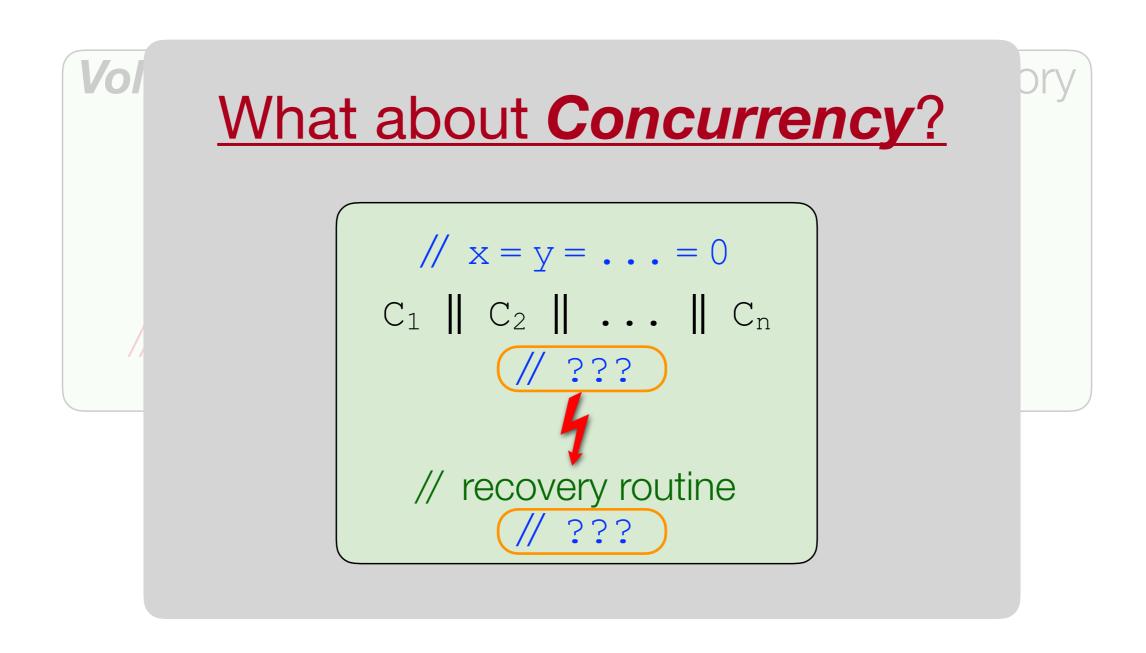

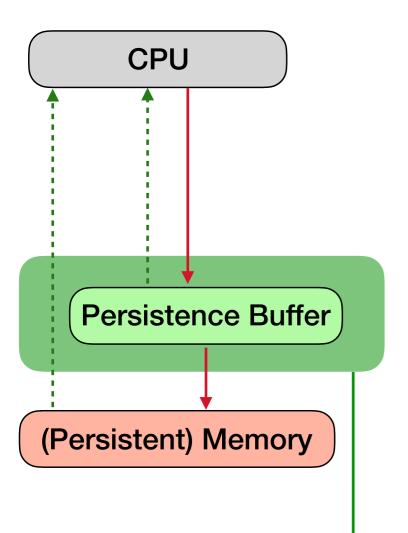

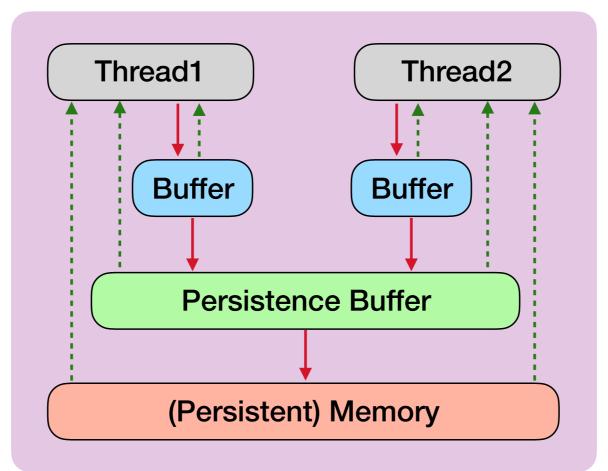

#### **Concurrent** Px86

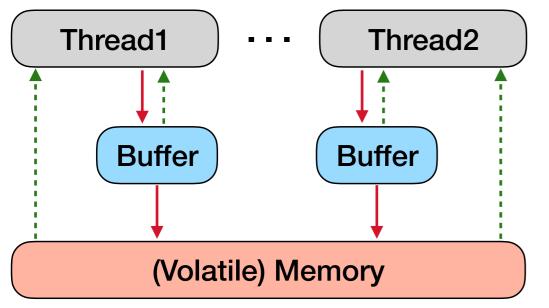

#### x86: (Volatile) Concurrent Hardware Model (TSO)

- x := 1 : adds x := 1 to buffer

- unbuffer\* : buffer to memory

- a:=x : if buffer contains x, reads latest entry else reads from memory

buffer and memory lost

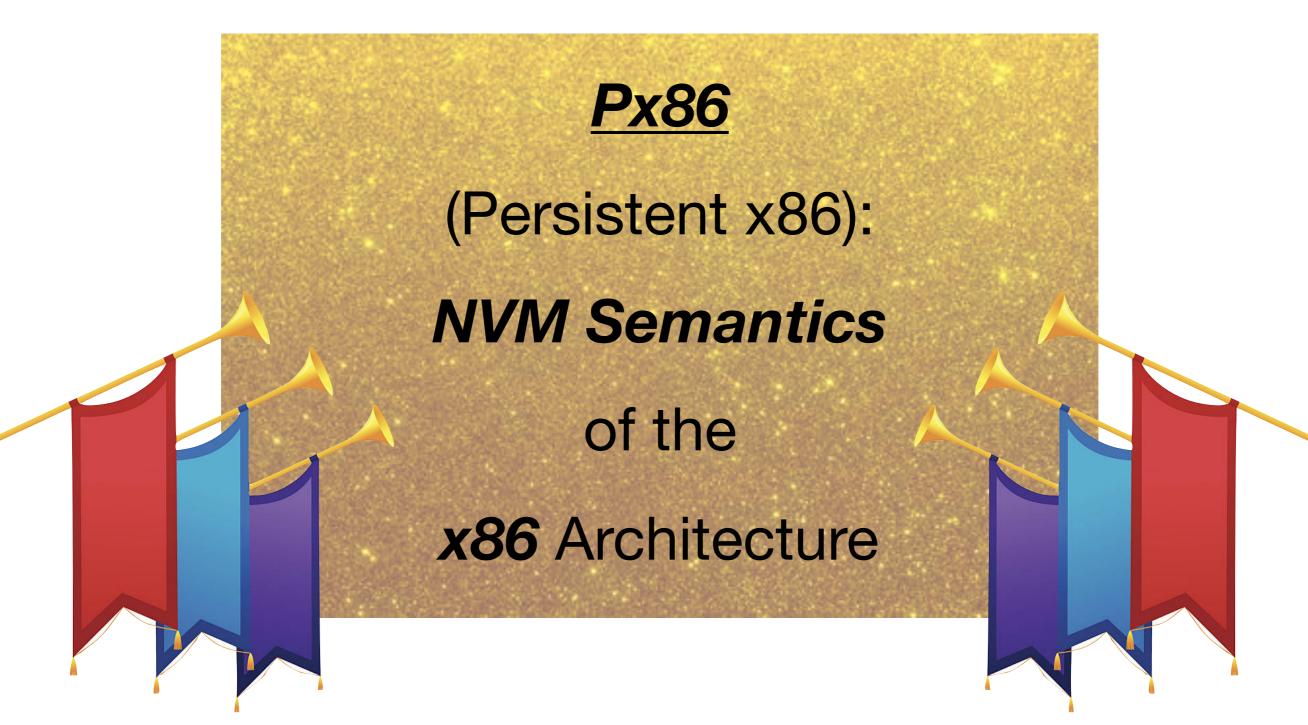

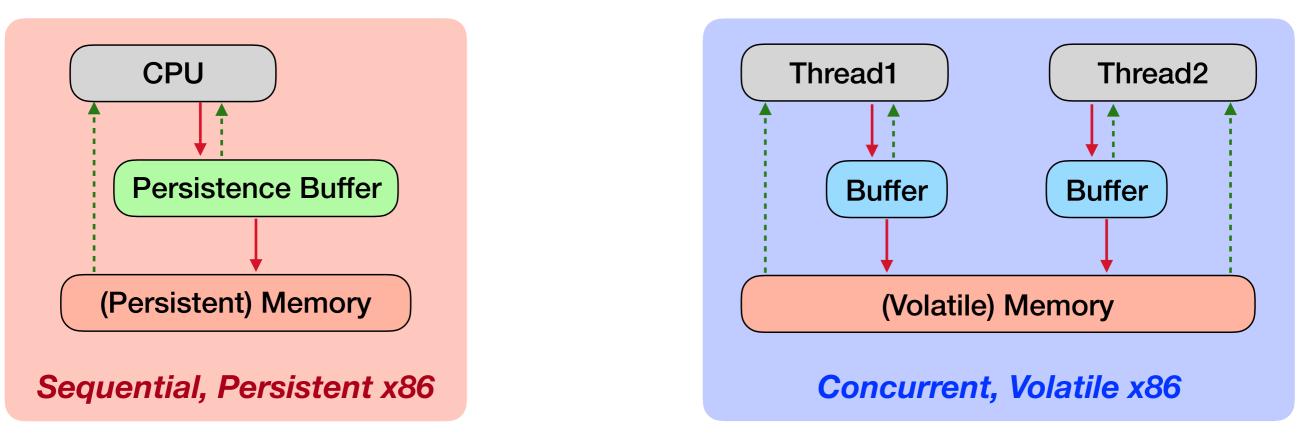

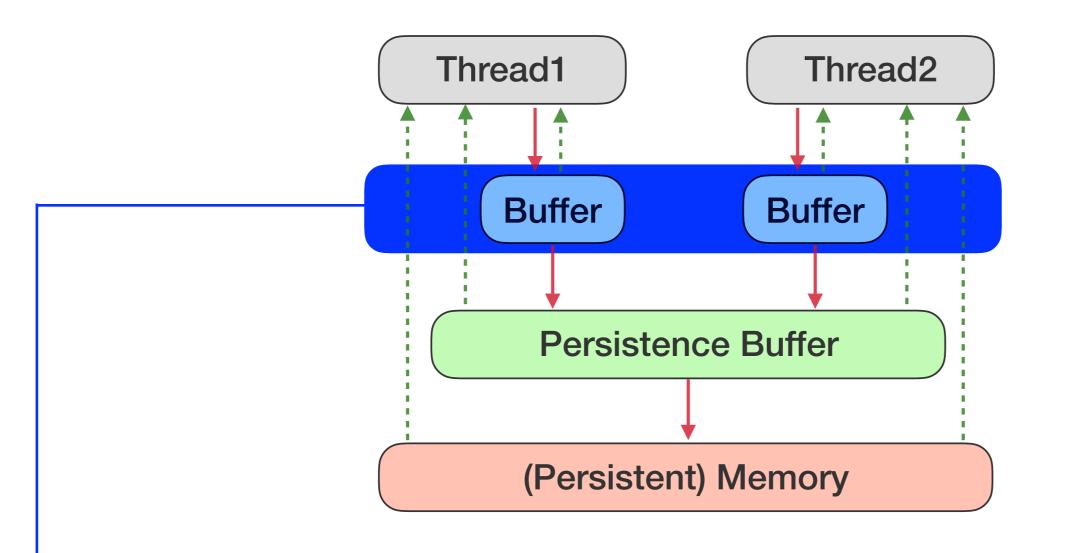

#### Px86: Persistent & Concurrent x86

### Persistent x86 (Px86)

buffer/unbuffer order: *consistency* model

### Persistent x86 (Px86)

### Persistent x86 (Px86)

#### Px86

#### Intel® Architecture Reference Manual

"Executions of the **clwb** instruction are ordered with respect to fence instructions ..."

"They are not ordered with respect to other executions of **clwb**, to executions of **clflush** and **clflushopt** ..."

# Ambiguities in text! ↓ Two Px86 models

#### Px86

#### Intel® Architecture Reference Manual

"Executions of the **clwb** instruction are ordered with respect to fence instructions ..."

"They are not ordered with respect to other executions of **clwb**, to executions of **clflush** and **clflushopt** ..."

#### *Ambiguities* in text! ↓ *Two* Px86 models

#### Px86<sub>man</sub>

- faithful to *manual* text

- weaker than architectural intent

- 2 models: operational & declarative proved equivalent

#### Px86<sub>sim</sub>

- captures architectural intent

- **stronger** than **manual** text

- 2 models: operational & declarative proved equivalent

# Summary

- ✓ Formalised Intel-x86 NVM semantics:

- + **Px86**man: equivalent operational & declarative models

- + **Px86**<sub>sim</sub>: equivalent operational & declarative models

- $\checkmark$  More in the paper

- ✤ Persistent transactional library implemented in Px86

- ✤ Persistent queue library implemented in Px86

- ? Future Work:

- ✤ program logics

- model checking algorithms

- ✤ litmus testing

# Summary

- ✓ Formalised Intel-x86 NVM semantics:

- + **Px86**man: equivalent operational & declarative models

- + **Px86**<sub>sim</sub>: equivalent operational & declarative models

- ✓ More in the paper

- ✤ Persistent transactional library implemented in Px86

- ✤ Persistent queue library implemented in Px86

- **?** Future Work:

- ✤ program logics

- model checking algorithms

- ✤ litmus testing

#### Thank You for Listening!

azalea@mpi-sws.org