# IsaBIL: A Framework for Verifying (In)correctness of Binaries in Isabelle/HOL

Matt Griffin

University of Surrey, Guildford, UK Imperial College London, UK

Brijesh Dongol ⊠ ©

University of Surrey, Guildford, UK

Azalea Raad ⊠ ©

Imperial College London, UK

#### Abstract

This paper presents IsaBIL, a binary analysis framework in Isabelle/HOL that is based on the widely used Binary Analysis Platform (BAP). Specifically, in IsaBIL, we formalise BAP's intermediate language, called BIL and integrate it with Hoare logic (to enable proofs of *correctness*) as well as incorrectness logic (to enable proofs of *incorrectness*). IsaBIL inherits the full flexibility of BAP, allowing us to verify binaries for a wide range of languages (C, C++, Rust), toolchains (LLVM, Ghidra) and target architectures (x86, RISC-V), and can also be used when the source code for a binary is unavailable.

To make verification tractable, we develop a number of big-step rules that combine BIL's existing small-step rules at different levels of abstraction to support reuse. We develop high-level reasoning rules for RISC-V instructions (our main target architecture) to further optimise verification. Additionally, we develop Isabelle proof tactics that exploit common patterns in C binaries for RISC-V to discharge large numbers of proof goals (often in the 100s) automatically. IsaBIL includes an Isabelle/ML based parser for BIL programs, allowing one to *automatically* generate the associated Isabelle/HOL program locale from a BAP output. Taken together, IsaBIL provides a highly flexible proof environment for program binaries. As examples, we prove correctness of key examples from the Joint Strike Fighter coding standards and the MITRE database.

2012 ACM Subject Classification Theory of computation  $\rightarrow$  Program reasoning

Keywords and phrases Binary Analysis Platform, Isabelle/HOL, Hoare Logic, Incorrectness Logic

Digital Object Identifier 10.4230/LIPIcs.ECOOP.2025.14

Related Version Extended Version: https://arxiv.org/abs/2504.16775 [21]

Supplementary Material Other (Isabelle/HOL): https://doi.org/10.5281/zenodo.15261359 [20]

Funding Brijesh Dongol: Supported by VeTSS and EPSRC grants EP/X037142/1, EP/X015149/1, EP/V038915/1, and EP/R025134/2.

Azalea Raad: Supported by the UKRI Future Leaders Fellowship MR/V024299/1, by the EPSRC grant EP/X037029/1 and by VeTSS.

#### 1 Introduction

Analysing binary code is highly challenging and is essential for decompilation and verification when one does not have access to the source code (e.g., proprietary code). It is also a key tool for finding security vulnerabilities and exploits and is often the only way to (dis)prove properties about programs [46]. Many tools for binary analysis such as angr [52], LIEF [49] and Manticore [36] lift machine code to higher-level, human-readable representations. These tools have been developed for different goals covering different languages (Rust, C++), hardware architectures (e.g., x86, RISC-V), types of binaries (ELF, smart contracts) and security analysis (malware analysis, reverse engineering).

The Binary Analysis Platform (BAP) [8] provides a generic approach to binary analysis. BAP natively supports several languages (C, Python and Rust) and hardware architectures (x86, Arm, RISC-V, MIPS) and additionally can be integrated with toolchains such as LLVM and Ghidra to analyse programs on less common architectures such as Atmel AVR [2]. BAP is well-supported and widely used with an active user community. The platform can analyse binaries derived from a particular source language such as C/C++ and Rust, as well as closed-source functions. BAP provides a disassembler that lifts binaries into a unified intermediate language called BIL (Binary Instruction Language), thus enabling architecture-agnostic analysis. While BAP also provides a set of static analysis tools, they do not provide mechanisms for formal verification, e.g., logics for (dis)proving correctness of programs. Recent works have covered subsets of BAP (called AIR) in UCLID5 [10] and use an extended semantics to enable reasoning about an information flow hyper-property known as trace-property observational determinism [10].

We present IsaBIL, a verification framework for low-level binaries encoded using the Isabelle/HOL theorem prover. IsaBIL provides a deep embedding of BIL programs into Isabelle/HOL, providing a direct interface between BAP and Isabelle/HOL without using any additional tools. We leverage the fact that BAP can generate BIL programs as abstract data types, providing a convenient hook for IsaBIL's ML-based parser. Since BAP can lift binaries into BIL both with and without the source code being available, so can IsaBIL. Moreover, IsaBIL allows the generated BIL program to be connected to any operational semantics. We build on the semantics described by [8] (see § 3) to enable bit-precise analysis. Our approach generates an Isabelle locale [27], which provides an extensible interface that can be instantiated to different scenarios (see Figure 2). We demonstrate this by both proving (using Hoare logic [23]) and disproving (using Incorrectness logic [42]) properties for a number of key examples (see Table 1).

| Table | 1 | ISABIL | examples | and | their | sizes. |

|-------|---|--------|----------|-----|-------|--------|

|       |   |        |          |     |       |        |

| Test            | Size (LoC) |        |      |          |  |

|-----------------|------------|--------|------|----------|--|

| Test            | C          | RISC-V | BIL  | Isabelle |  |

| AV Rule 17      | 13         | 34     | 80   | 94       |  |

| AV Rule 19      | 10         | 16     | 36   | 64       |  |

| AV Rule 20      | 18         | 52     | 118  | 393      |  |

| AV Rule 21      | 16         | 45     | 105  | 210      |  |

| AV Rule 23      | 11         | 35     | 81   | 90       |  |

| AV Rule 24      | 15         | 40     | 107  | 74       |  |

| AV Rule 25      | 24         | 99     | 233  | 578      |  |

| DF (good)       | 27         | 19     | 44   | 366      |  |

| DF (bad)        | 27         | 19     | 43   | 171      |  |

| read_data (bad) | 74         | 131    | 296  | 474      |  |

| sec_recv (bad)  | 38         | 122    | 272  | 752      |  |

| Total           | 273        | 612    | 1415 | 3266     |  |

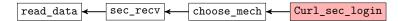

**Scalability.** Our approach is *compositional* in that we can analyse and (dis)prove properties about a *code fragment*, say a function f, in isolation and then reuse these properties (without reproving them) in bigger contexts where f is used. To show this, we use our technique to detect (using incorrectness logic) a double-free vulnerability in the cURL library (used primarily for transferring data over the internet). As we demonstrate in § 7, although this

<sup>&</sup>lt;sup>1</sup> Note that this is a significant advancement over the encoding by Griffin and Dongol [19], which used an external Python tool to translate BAP outputs to Isabelle/HOL.

vulnerability is "hidden" in an internal function (not exposed in a header file) and is not visible to client applications, it is accessible by a call chain (comprising four separate functions) that can be triggered from an external function, i.e. it is accessible from within a client application and thus this vulnerability can be easily exploited. Indeed, this vulnerability has been previously documented as CVE-2016-8619.

Contributions. Our main contributions are as follows. (1) We develop IsaBIL, a flexible, semi-automated tool for verifying binaries (lifted to BIL) within the Isabelle/HOL theorem prover. Our mechanisation is complete with respect to the BIL language and semantics. During the mechanisation, we uncovered and fixed several inconsistencies in the official BAP documentation (see §3). (2) We developed IsaBIL as a highly flexible and extensible system (see Figure 2) using Isabelle locales [3, 27]. We incorporate logics for (in)correctness, thus obtain methods for both proving and disproving properties. To the best of our knowledge, this is the first application of Incorrectness logic [42] in the analysis of low-level binaries. (3) We extend IsaBIL with a number of automation techniques, including reusable high-level big-step theorems, proof tactics that automatically discharge large numbers of proof goals, and architecture-specific proof optimisations. We also include a native parser for  $BIL_{ADT}$ programs, written in Isabelle/ML, to automatically transpile BAP outputs to an Isabelle/HOL locale suitable for verification. (4) We apply our methods to a number of examples (see Table 1), including key tests from the Joint Strike Fighter (JSF) C++ Coding Standards [32]. (5) We show the scalability of IsaBIL by detecting a double-free vulnerability in a large example (253 assembly LoC) in the cURL library.

## 2 Motivation and Workflow

In this section, we motivate our work and provide an overview of our overall approach using two running examples. We give the C program and their equivalent BIL in §2.1. We present our workflow and an overview of the Isabelle/HOL mechanisation in §2.2.

#### 2.1 Two C programs and their BIL representations

We motivate our analysis using two variations of a double-free vulnerability (listed as CWE-415 in the MITRE database<sup>2</sup>). A double-free error occurs when a program calls free twice with the same argument. This may cause two later calls to malloc to return the same pointer, potentially giving an attacker control over the data written to memory.

The occurrence of the double-free vulnerability is straightforward to see in Listing 1, but of course, in a real program, the vulnerability may be much more difficult to identify. Listing 2 presents an alternative program that contains two occurrences of free(p) with no intervening malloc. However, Listing 2 does not contain a double-free vulnerability since the true branch returns from the method call before the second free(p) is executed.

https://cwe.mitre.org/data/definitions/415.html

```

Listing 3 Pretty printed BIL of Listing 1.

Listing 4 Pretty printed BIL of Listing 2.

sub bad(bad_result)

sub good(good_result)

X10 := 0x2A

X10 := 0x2A

@malloc

@malloc

oc with return 5

with [X8 - 0x18, el]:u64 <- X10

mem := mem

mem := mem

with [X8 - 0x18, el]:u64 <- X10

X15 := mem[X3 - 0x7C8, e1]:u32

X15 := mem[X3 - 0x7C8, e1]:u32

when (X15 = 0) goto 13

when (X15 = 0) goto 13

goto 10

goto 10

10 X10 :=

mem[X8 - 0x18, el]:u64

10 X10 :=

mem[X8 - 0x18, el]:u64

call Ofree with return 13

call Ofree with return 16

13 X10 :=

mem[X8 - 0x18, el]:u64

13 X10 :=

mem[X8 - 0x18, el]:u64

call Ofree with return 16

call Ofree with return 16

16 call X1 with noreturn

16 call X1 with noreturn

```

```

*.c/Compiler *.exe BAP *.bil IsaBIL correctness proof [42]

```

Figure 1 Translation of C source programs to an Isabelle/HOL proof.

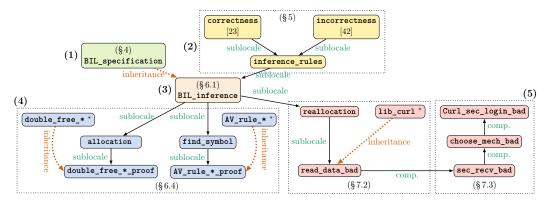

Figure 2 Structure of IsaBIL locales: theories indicated by \* are auto-generated from a given \*.bil file following the translation in Figure 1.

The focus of our work is to analyse such programs without relying on any high-level language semantics. Instead, we aim to develop a technique for reasoning about programs (e.g., those in Listings 1 and 2) at a lower level of abstraction by first compiling the programs then, lifting the resulting binaries to an intermediate representation (BIL). Although such analysis contains more detail, the analysis reflects the behaviour of the actual executable, thus is more accurate (e.g., does not require any additional compiler correctness assumptions).

## 2.2 Workflow and Mechanisation

Our overall workflow is given in Figure 1, where the dashed steps represent existing work. The first step to proving properties about our example program is to use BAP to generate a BIL representation of a binary executable (see Figure 1). For our example program in Listings 1 and 2, the BIL equivalent (expressed in BIR format) are given in Listings 3 and 4, respectively. BIR (Binary Intermediate Representation) is a structured refinement of BIL that significantly enhances human readability by presenting sequences of BIL as a

single instruction. Take for example the BIR instruction call @free with return 18 on line 16 in Listings 3 and 4. This represents two BIL statements, a jump to the address of the symbol "free", and the assignment of the return value 18 to the return pointer. Note that IsaBIL takes as input BAP's abstract data type format (see § 4), which we refer to as BIL<sub>ADT</sub>, as opposed to the human-readable forms shown in Listings 3 and 4. This makes the BIL instructions simpler to parse when generating the corresponding Isabelle/HOL object (discussed in more detail below).

Extensions to Isabelle/HOL's logic [15, 5, 26, 18] often make use of Isabelle/HOL's locale system [27, 3], which provides convenient modules for building parametric theories. Locales are aimed at supporting the use of local assumptions and definitions for collections of similar theories, defined in terms of fixed variables and definitions. We refer to the fixed variables as parameters which must satisfy the local assumptions. For a locale  $\mathcal{L}$ , we give its definition as  $\mathcal{L} = (p_1, p_2, \dots)$  where  $p_1, p_2$  are the parameters of the locale. Each parameter may be any type derived from a set or a relation. From these variables, assumptions and definitions we can derive general theorems within the context of a locale. These theorems can be exported to the current proof context by *instantiation*, in which we provide values to one or all of the parameters and verify the fixed assumptions of these parameters. This effectively gives us the general theorems contained within each locale for free for a specific instantiation. Locales can be extended through *inheritance* or *interpretation*, enabling reusability and specialisation by introducing and refining a locale's parameters. Inheritance operates hierarchically, directly propagating the context of a parent locale to a child locale. This transfer includes general theorems, assumptions, definitions and fixed variables. Interpretation is compositional, associating a locale or definition with another locale. During interpretation, the assumptions of the parent locale must be satisfied as part of the mapping process. A locale that interprets another locale is referred to as a sublocale, denoted  $\mathcal{L} \subseteq \mathcal{L}'$ , where locale  $\mathcal{L}'$  is the parent of L. For IsaBIL, they provide a uniform system for representing both the program, and the underlying reasoning framework.

The overall structure of the IsaBIL development is given in Figure 2, and comprises four main parts (which highlight our four main contributions). Overall, we have: (1) a locale (see § 4), representing a complete formalisation of the BIL specification from § 3, (2) a set of locales (see § 5) that encode Hoare Logic (to verify correctness) and Incorrectness Logic (as developed by O'Hearn), (3) a locale (see § 6.1) that combines formalisation of the BIL specification with (in)correctness logics, (4) a set of locales (see § 6.4) that apply the resulting verification framework to prove correctness of a number of examples from the literature and (5) a set of locales (see § 7.2 and 7.3) that demonstrate scalability of the approach. In particular, § 7.2 demonstrates the use of subroutines to enable one to focus on key functions of interest, even when starting with large BIL files (> 100k LoC). Then § 7.3 describes how verified subroutines can be used as subcomponents to prove (in)correctness of a larger system.

Our framework is highly flexible and extensible. For instance, the BIL\_inference locale combines the BIL\_specification and inference\_rules locales. In case one wishes to change the specification (for a different operational semantics), or use a different set of inference rules (to perform a type of analysis), one can simply change the specification and/or inference rule locales. Similarly, a locale can be extended with additional semantic features: our proofs extend the BIL\_inference locale with an allocation locale (that models memory allocation) and a find\_symbol locale (that tracks a symbol table) to enable reasoning about different program features.

Our encoding of BIL (§ 4) is the *first* full mechanisation of BIL in Isabelle/HOL. This mechanisation is a standalone contribution and can be used by others outside of our reasoning framework. Our encoding uncovers some inconsistencies in the official specification, which are addressed by the mechanisation (see § 3). Moreover, given that BIL is an intermediate language for many different architectures, future versions could be further optimised to a particular architecture. As an example, we present optimisations for RISC-V (see § 6.2.3), which is the architecture that we focus on.

To maximise flexibility, we provide an encoding of the inference rules parameterised by an operational semantics, i.e., an *instance* of the correctness and incorrectness rules can be generated for *any* operational semantics. This instance automatically inherits all of the rules of Hoare and Incorrectness logic that we prove generically in the **correctness** and **incorrectness** locales (§ 5).

The BIL semantics from § 4 and the inference rules from § 5 are combined to form a new locale, BIL\_inference, which provides facilities to verify BIL programs. Then, as discussed above, to verify particular types of examples, we extend the locales with models of allocation and symbols to verify particular sets of examples. These proofs represent the *first* proofs of both correctness and incorrectness for BIL programs in Isabelle/HOL. As we shall see in § 3, the BIL semantics is highly detailed, with the reductions related to even single load command potentially splitting into a large number of *small-step* transitions. This has the potential to increase the verification complexity making the proofs of even small programs intractable. To address this, we use BIL's big-step semantics (§ 6.1) and introduce a number of high-level lemmas that allow one to discharge such proofs generically. These lemmas are reusable across all of the examples that we verify.

Our proofs cover key examples from the JSF coding standards [32] and the CWE database<sup>2</sup>. This task is greatly simplified using IsaBIL's parser, written in Isabelle/ML [50], that automatically generates a locale corresponding to a BIL program written in BIL<sub>ADT</sub> format. Note that Isabelle isolates Isabelle/ML programming, and hence our parser cannot interfere with soundness of Isabelle's core logic engine. The generated locale is then combined with BIL\_inference to provide a context in which (in)correctness proofs can be carried out.

# 3 BIL Syntax and Semantics

Before proceeding with the presentation of our proofs, it is essential to acquire a basic understanding of BIL. This section serves as a succinct introduction to BIL, emphasizing its type system, memory model and operational semantics. We encourage interested readers to explore the BIL manual [8].

## 3.1 Syntax

The basic syntax of BIL programs is given in Figure 3.

**Statements.** A BIL statement may assign an expression e to a variable var, transfer control to a given address e, interrupt the CPU with a given interrupt num, be an instruction with unknown semantics, a while loop, or an if-then-else conditional (with an optional else clause). Note that each BIL statement (including a compound statement) corresponds to a single machine instruction, thus side effects such as setting a status register must be captured in the statement definition (see § 3.4).

**Statements**, where str denotes a string (of type string) and  $i \in \mathbb{Z}$

```

stmt \ni s ::= var := e \mid \mathbf{jmp} \mid e \mid \mathbf{cpuexn}(i) \mid \mathbf{special}(str) \mid \mathbf{while} \mid (e) \mid seq \mid \mathbf{if} \mid (e) \mid seq \mid \mathbf{if} \mid (e) \mid seq_1 \mid else \mid seq_2

bil \ni seq ::= stmt^*

```

**Expressions**, where id denotes a variable name literal (of type string)

```

exp \ni e ::= v \mid var \mid e_1[e_2, ed] : sz \mid e_1 \text{ with } [e_2, ed] : sz \leftarrow e_3 \mid e_1 \text{ bop } e_2 \mid uop \ e

\mid cast : sz[e] \mid \mathbf{let} \ var = e_1 \ \mathbf{in} \ e_2 \mid \mathbf{ite} \ e_1 \ e_2 \ e_3 \mid e_1 \ @ \ e_2 \mid \mathbf{extract} : sz_1 : sz_2[e]

bop ::= aop \mid lop \quad var ::= id : type \quad endian \ni ed ::= \mathbf{el} \mid \mathbf{be}

cast ::= \mathbf{low} \mid \mathbf{high} \mid \mathbf{signed} \mid \mathbf{unsigned}

```

*Types and Values*, where  $sz, nat \in \mathbb{N}$

```

type \ni t ::= \mathbf{imm} \langle sz \rangle \mid \mathbf{mem} \langle sz_{addr}, sz_{val} \rangle word \ni w ::= nat :: sz value \ni v ::= w \mid v[w \leftarrow v', sz_{val}] \mid \mathbf{unknown}[str] : t

```

**Figure 3** BIL syntax and types.

**Expressions.** Memory loads and stores are represented at the expression level as  $e_1[e_2,ed]: sz$  for loads, and  $e_1$  with  $[e_2,ed]: sz \leftarrow e_3$  for stores. In these expressions, the evaluation of  $e_1$  represents the target storage being accessed, while the evaluation of  $e_2$  specifies the address. Since a memory operation can span multiple addresses, both the endianess (ed) and the size (sz) of the operation are provided. For stores, the evaluated value of  $e_3$  is written to memory at the given address. Binary operations now differentiate arithmetic (aop) and logical (lop) operations. Expressions in BIL also include casts, let bindings, if-then-else expressions, concatenations and extractions. The extraction operation, denoted as  $extract: sz_1: sz_2[e]$ , first evaluates the expression e to a word e and then extracts a slice from e using BIL's existing extraction mechanism. Specifically,  $ext \ w \sim hi: sz_1 \sim ho: sz_2$  represents the bits of e from bit e to bit e to bit e to a vord e and are evaluated wrt a state e to e to e to e to e to e using specifically. Expressions are side-effect free and are evaluated wrt a state e to e

**Types and Values.** The highly expressible nature of BIL is due to its type system, which defines two distinct types for its values, the irreducible subset of a BIL expression. These types are  $\mathbf{imm}\langle sz\rangle$  (describing an  $immediate\ type$  of size sz) and  $\mathbf{mem}\langle sz_{addr},\ sz_{val}\rangle$  (describing a  $storage\ type$  with address size  $sz_{addr}$  and value size  $sz_{val}$ ). A value can be bound to one of the three possibilities. (1) A machine word (w). (2) An abstract storage  $(v[w\leftarrow v',\ sz_{val}])$ , which allows us to define a memory as a chain of mappings, where  $[w\leftarrow v',sz_{val}]$  defines a single mapping from an address (w) to a value (v') of size  $sz_{val}$ . Here, v could either be the root of the chain (in which case it is  $\mathbf{unknown}[str]:t$ ) or another storage. Technically, v could also be a word, but we disallow this by introducing a typing context (see below). Similarly, v' could be a storage according to the grammar, but this possibility is also eliminated by the typing context. When v or v' is an unknown value, we require that type of v is  $\mathbf{mem}$  and the type of v' is  $\mathbf{imm}$ . (3) An "unknown" value  $(\mathbf{unknown}[str]:t)$ , which is obtained from the evaluation of a BIL expression holding some string information str of some type t.

The type of a value can be obtained using the function type, which is define as follows:

```

\begin{aligned} \mathsf{type}(nat :: sz) &= \mathbf{imm} \langle sz \rangle \\ \mathsf{type}(v[(nat :: sz_{addr}) \leftarrow v', \ sz_{val}]) &= \mathbf{mem} \langle sz_{addr}, \ sz_{val} \rangle \\ \mathsf{type}(\mathbf{unknown}[str] : t) &= t \end{aligned}

```

In [21] we show the lifted BIL equivalent of a RISC-V program using the syntax presented in this section.

# 3.2 Typing Rules and Typing Context

BIL's type system facilitates the need for typing rules to ensure type correctness. At the lowest level, the rules ensure that types are correctly defined with the predicate t is ok. The type of variables must be tracked during symbolic execution to ensure that they do not change and only values of the correct type can be assigned. This is achieved via a typing context, defined as  $\Gamma ::= var^*$ , where type correctness of  $\Gamma$  is expressed by overloading the predicate  $\Gamma$  is ok. The rules for t is ok and  $\Gamma$  is ok are given below:

These are extended to expressions, then to the level of statements (see [8] for details). As part of our formalisation, we discover a missing typing rule for empty sequences, which would otherwise be needed to ensure the sequencing rules are type correct. We have created a pull request in the BAP repositories for this issue (see https://github.com/BinaryAnalysisPlatform/bap/pull/1588), which has now been merged.

# 3.3 Expression Semantics

Expression evaluation requires the repeated application of small-step semantics rules until the expression is reduced to a value. An expression step in BIL is formally expressed with the  $\Delta \vdash e \leadsto e'$ , where multiple steps can be reduced using the reflexive transitive closure  $\Delta \vdash e \leadsto^* e'$ . Recall that loads and stores occur at the expression level, and are sensitive to endian orderings. We provide the load rules here, and refer the interested reader to the BIL manual [8] for further details.

A store instruction (semantics not shown) targets a single unit of addressable memory, typically 8-bits in size. When a storage operation exceeds this size, it is converted into a sequence of 8-bit stores, organised in big-endian order. The reduction rules for load operations is given in Figure 4. First, all sub-expressions of a memory object are reduced to values using the rules LOAD\_STEP\_ADDR and LOAD\_STEP\_MEM. Then, the resulting object is recursively deconstructed using the LOAD\_WORD\_EL and LOAD\_WORD\_BE rules, depending on the endian. This process continues until one of LOAD\_BYTE, LOAD\_UN\_MEM or LOAD\_UN\_ADDR is used. LOAD\_BYTE reduces the expression to the value, v', when the memory object is a storage of an immediate (known) value, w. LOAD\_UN\_MEM and LOAD\_UN\_ADDR both reduce the expression to an unknown value when the memory or address being loaded is unknown, respectively.

▶ Example 1. Consider the instruction, X10 := mem[X8-0x18, e1]:u64, from line 12 in Listing 3, which performs a little-endian load of a 64-bit word from address X8-0x18 in the variable mem. We first reduce the address expression, X8-0x18, to a value using LOAD\_STEP\_ADDR, next we apply LOAD\_STEP\_MEM to read the value stored in mem. Next,

$$\begin{array}{l} (\text{VAR\_IN}) & (\text{LOAD\_STEP\_ADDR}) \\ (var, v) \in \Delta \\ \hline \Delta \vdash var \leadsto v \end{array} & \begin{array}{l} \Delta \vdash e_2 \leadsto e_2' \\ \hline \Delta \vdash e_1[e_2, ed] : sz \end{array} & \begin{array}{l} \Delta \vdash e_1 \leadsto e_1' \\ \hline \Delta \vdash v[e_2, ed] : sz \end{array} & \begin{array}{l} \Delta \vdash e_1 \bowtie e_2' \\ \hline \Delta \vdash v[e_2, ed] : sz \end{array} & \begin{array}{l} \Delta \vdash e_1 \bowtie e_2' \\ \hline \Delta \vdash v[w \leftarrow v', sz][w, ed] : sz \leadsto v' \end{array} & \begin{array}{l} (\text{LOAD\_BYTE\_FROM\_NEXT}) \\ \hline \Delta \vdash v[w \leftarrow v', sz][w, ed] : sz \leadsto v' \end{array} & \begin{array}{l} (\text{LOAD\_BYTE\_FROM\_NEXT}) \\ \hline \Delta \vdash v[w_1 \leftarrow v', sz][w_2, ed] : sz \leadsto v[w_2, ed] : sz \\ \hline (\text{LOAD\_UN\_MEM}) \\ \hline \Delta \vdash (\text{unknown}[str] : t)[v, ed] : sz \leadsto \\ \text{unknown}[str] : \text{imm} \langle sz \rangle \end{array} & \begin{array}{l} (\text{LOAD\_UN\_ADDR}) \\ \hline \Delta \vdash v[w_1 \leftarrow v', sz'][\text{unknown}[str] : t, ed] : sz \leadsto \\ \text{unknown}[str] : \text{imm} \langle sz \rangle \end{array} & \begin{array}{l} (\text{LOAD\_WORD\_BE}) \\ sz \gg sz_{mem} \quad \text{succ}(w) = w' \\ \text{type}(v) = \text{mem} \langle sz_{addr}, sz_{mem} \rangle \\ \hline \Delta \vdash v[w, \text{be}] : sz \leadsto \\ v[w, \text{be}] : sz_{mem} @ v[w', \text{be}] : (sz - sz_{mem}) & v[w', \text{el}] : (sz - sz_{mem}) @ v[w, \text{el}] : sz_{mem} \end{array} & \begin{array}{l} (\text{LOAD\_WORD\_EL}) \\ sz \gg sz_{mem} \quad \text{succ}(w) = w' \\ \text{type}(v) = \text{mem} \langle sz_{addr}, sz_{mem} \rangle \\ \hline \Delta \vdash v[w, \text{el}] : sz \leadsto \\ v[w', \text{el}] : (sz - sz_{mem}) @ v[w, \text{el}] : sz_{mem} \end{array} & \begin{array}{l} (\text{LOAD\_VORD\_EL}) \\ \text{Summ} & \text{Succ}(w) = w' \\ \text{Summ} & \text{Summ} & \text{Succ}(w) = w' \\ \text{Summ} & \text{Summ} & \text{Summ} & \text{Summ} \\ \text{Summ} & \text{Summ} & \text{Summ} & \text{Summ} & \text{Summ} \\ \text{Summ} & \text{Summ} & \text{Summ} & \text{Summ} & \text{Summ} \\ \text{Summ} & \text{Summ} & \text{Summ} & \text{Summ} & \text{Summ} \\ \text{Summ} & \text{Summ} & \text{Summ} & \text{Summ} & \text{Summ} \\ \text{Summ} & \text{Summ} & \text{Summ} & \text{Summ} & \text{Summ} \\ \text{Summ} & \text{Summ} & \text{Summ} & \text{Summ} & \text{Summ} \\ \text{Summ} & \text{Summ} & \text{Summ} & \text{Summ} & \text{Summ} \\ \text$$

**Figure 4** Reduction rules for Load.

we look up the value of mem in  $\Delta$  in VAR\_IN, which reduces mem to the corresponding storage. Next, we apply LOAD\_WORD\_EL to break down the 64-bit load into 8 separate loads in little-endian format. Each of the 8 byte-sized loads are individually read from memory using LOAD\_BYTE and LOAD\_BYTE\_FROM\_NEXT. Finally, we apply BIL's concatenation rule (not shown) to join each byte into a single 64-bit word.

IsaBIL Extensions. The previous sections present a summary of BIL's semantics from the BIL manual [8] with some minor corrections. In this section, we present extensions to BIL's big-step expression evaluation semantics. The reduction of expressions, e.g., in load and store instructions, results in a significant proof burden. To make verification tractable, IsaBIL defines additional big-step expression evaluation rules which are derived from a combination of BIL's existing small-step and big-step expression semantics. For example, the load expression in Example 1 requires the repeated application of over 150 small-step rules. Splitting the 64-bit read into individual reads in Example 1 (from LOAD\_WORD\_EL onwards) and the concatenation of the result can be combined into a single big-step rule. We first provide some syntactic sugar for a storage whose size is a multiple of 8.

The definition uses the function  $\mathtt{succ}(w)$ , which retrieves the successor of the word w such that  $\mathtt{succ}(w) := w+1$ . Furthermore, we use  $\mathtt{storage}_{en}\left(v,w,v',N\right)$  to refer to a contiguous storage of the value v' of size  $N \in \{8i \mid i \in \mathbb{N}\}$  (i.e., N is a multiple of 8) at address w on the storage v:

$$\begin{split} & \operatorname{storage}_{\mathbf{el}}\left(v, w, v', N\right) \doteq \begin{cases} \operatorname{storage}_{\mathbf{el}}\left(v[w \leftarrow \operatorname{ext}\ v' \backsim \operatorname{hi}: 7 \backsim \operatorname{lo}: 0,\ 8], \\ \operatorname{succ}(w), \operatorname{ext}\ v' \backsim \operatorname{hi}: N - 1 \backsim \operatorname{lo}: 8, N - 8 \end{cases} & \text{if } N > 8 \\ v[w \leftarrow v',\ 8] & \text{otherwise} \end{cases} \\ & \operatorname{storage}_{\mathbf{be}}\left(v[w \leftarrow \operatorname{ext}\ v' \backsim \operatorname{hi}: N - 1 \backsim \operatorname{lo}: N - 8,\ 8], \\ \operatorname{succ}(w), \operatorname{ext}\ v' \backsim \operatorname{hi}: N - 9 \backsim \operatorname{lo}: 0, N - 8 \end{cases} & \text{if } N > 8 \end{cases} \\ & v[w \leftarrow v',\ 8] & \text{otherwise} \end{cases} \end{aligned}$$

For example, suppose  $B_1$  and  $B_2$  are two 8-bit words. We have:

$$storage_{el}(v, w, B_1B_2, 16) = v[w \leftarrow B_2, 8][succ(w) \leftarrow B_1, 8]$$

$storage_{el}(v, w, B_1B_2, 16) = v[w \leftarrow B_1, 8][succ(w) \leftarrow B_2, 8]$

We give a subset of these rules for little endian 64-bit load and store operations below.

$$\frac{\left(\texttt{REFL\_LOAD\_EL\_WORD64}\right)}{\Delta \vdash \texttt{storage}_{\textbf{el}}\left(v, w_2, w_1, 64\right)\left[w_2, 64\right] : \textbf{el} \leadsto^* w_1}{\Delta \vdash v \ \textbf{with} \ \left[w_2, \textbf{el}\right] : 64 \leftarrow w_1 \leadsto^* \\ \texttt{storage}_{\textbf{el}}\left(v, w_2, w_1, 64\right)}$$

**Example 2.** Consider the load from Example 1. The first few steps proceed as before. However, instead of applying LOAD\_WORD\_EL, we can directly apply REFL\_LOAD\_EL\_WORD64 to obtain the corresponding value  $\Delta \vdash (\mathtt{storage_{el}}(v, w, v', 64))[w, el] : u64 \leadsto^* v'$ .

All big-step rules from this section, such as REFL\_LOAD\_EL\_WORD64 have been verified in Isabelle wrt to the small step semantics.

# 3.4 Statement semantics

In this section, we describe the operational semantics for evaluating statements. We also provide a correction to the sequencing rule from the manual [4]. Although each statement induces local control flow, in BIL, they are assumed to execute to completion in a single step.

The semantics of a statement is defined by  $(\Delta, pc) \vdash seq \leadsto (\Delta', pc')$ , which executes the *bil* statement seq from the variable store  $\Delta$  to generate a new variable store  $\Delta'$  and program counter pc'. The MOVE statement (see below) modifies  $\Delta$  by generating a new variable binding, and JMP (not shown) affects program counter.

Example rules for Move (aka assignment) and IF\_TRUE (for branching on a true guard are given below). In the move rule, the given expression e is evaluated to a value using the big-step semantics, and the value for the given variable var is updated in the variable state. In the IF\_TRUE rule, the guard is evaluated (to true) then the statement  $seq_1$  is executed. The sequencing rules describe execution of a list of statements to completion. The sequencing rules in manual [4] do not provide a means to reduce multiple statements in a single transition<sup>3</sup>.

$$\frac{\Delta \vdash e \leadsto^* v}{(\Delta, \ pc) \vdash var := e \leadsto (\Delta(var \mapsto v), \ pc)} \frac{\Delta \vdash e \leadsto^* true}{\Delta \vdash e \leadsto^* true} \frac{(\Delta, pc) \vdash seq_1 \leadsto (\Delta', pc')}{(\Delta, \ pc) \vdash if \ (e) \ seq_1 \ else \ seq_2 \leadsto (\Delta', \ pc')}$$

$$\frac{(\text{SEQ\_REC})}{(\Delta_1, \ pc_1) \vdash s_1 \leadsto (\Delta_2, \ pc_2)} \frac{(\Delta, pc_2) \vdash s_2 \dots s_n \leadsto (\Delta_3, pc_3)}{(\Delta_1, pc_1) \vdash s_1 s_2 \dots s_n \leadsto (\Delta_3, pc_3)} \frac{(\text{SEQ\_NIL})}{(\Delta, pc) \vdash \varepsilon \leadsto (\Delta, pc)}$$

▶ **Example 3.** Consider the load expression from Example 1, which appears on the right-hand side of the assignment statement given below:

$$(\Delta, (12 :: 64) + (1 :: 64)) \vdash \{X10 := mem[X8-0x18, el] : u64\} \rightsquigarrow (\Delta(X10 \mapsto v'), (13 :: 64))$$

To apply the statement semantics, we start by deconstructing it using SEQ\_REC, which results in two sub-steps. For the first, we apply MOVE and the steps in Example 1 to reduce the expression mem[X8-0x18,el]:u64 to a value, v'. Since the original sequence only contained a single statement, our recursive sequence (i.e., the second premise of SEQ\_REC) is empty, which can be trivially reduced using SEQ\_NIL.

We have created a Git pull request in the BAP repositories for this issue (https://github.com/BinaryAnalysisPlatform/bil/pull/12.

#### 3.5 BIL Step Relation

A machine instruction in BIL is represented by a named tuple,  $insn = \{ addr, size, code \}$  (implemented later as an Isabelle record). Here addr, refers to the instruction's address in memory; size, the size of the instruction; and code, the semantics of the program represented by BIL statements. Instructions operate over the BIL machine state,  $(\Delta, pc, mem)$ , where  $\Delta$  is the variable store, pc is the program counter and mem is a variable that denotes the memory. To decode the current instruction from a machine state, we assume an uninterpreted  $\mapsto$  function, referred to as the  $decode\ predicate$ , which maps a machine state,  $(\Delta, pc, mem)$ , to the corresponding instruction,  $\{ addr, size, code \}$ . The BIL step relation  $(\Delta, pc, mem) \rightsquigarrow (\Delta', pc', mem')$  defines the execution of a single BIL statement:

```

\frac{(\Delta, pc, mem) \mapsto (\mathbf{addr} = pc, \mathbf{size} = z, \mathbf{code} = bil) \qquad (\Delta, pc + z) \vdash bil \leadsto (\Delta', pc')}{(\Delta, pc, mem) \leadsto (\Delta', pc', mem)}

```

▶ **Example 4.** Consider the move statement from Example 3, which resides at the program address 12 and being of one-byte size. This is expressed as the BIL instruction below:

```

\| \mathbf{addr} = 12 :: 64, \mathbf{size} = 1 :: 64, \mathbf{code} = \{ X10 := mem[X8-0x18, el] : u64 \} \|

```

The instruction is obtained by decoding  $(\mapsto)$  a machine state of the form  $(\Delta, 12 :: 64, mem)$  where  $X8, mem \in dom(\Delta)$ . By using decode we can structure a step proof for the machine state as follows:

```

(\Delta, 12 :: 64, mem) \sim (\Delta(X10 \mapsto v'), 13 :: 64, mem)

```

By applying the STEP\_PROG rule for programs, we are left with a reduction  $(\Delta, (12 :: 64) + (1 :: 64)) \vdash \{\texttt{X10} := \texttt{mem}[\texttt{X8-0x18}, \texttt{el}] : \texttt{u64}\} \rightsquigarrow (\Delta(X10 \mapsto v'), (13 :: 64))$ , which we derived in Example 3.

# 4 Mechanisation

In this section, we describe the IsaBIL mechanisation, which utilises extensible *locales* to maximize reusability. In § 4.1, we describe the generic BIL\_specification locale that formalises BIL's syntax and semantics, and in § 4.2 we describe the IsaBIL translation tool that automatically generates locales from BIL programs.

#### 4.1 The BIL\_specification Locale

IsaBIL's BIL\_specification locale (see Figure 2) provides a complete mechanisation of BIL's syntax and semantics<sup>4</sup>. We encode BIL's operational rules (§ 3.5) as Isabelle's built-in *inductive predicates*, which allow one to formalise the structure of the syntax from Figure 3.

The BIL\_specification =  $(\mapsto)$  locale provides a single parameter: the *decode* predicate  $(\mapsto)$ , which will be uniquely instantiated for each binary that we wish to verify.

We provide rules for both *introduction* (which are used to introduce compound statements such as **if-then-else** to the proof goal) as well as *elimination* (which are used to eliminate compound statements from the proof assumptions) directly within the BIL\_specification locale. For example, introduction and elimination rules for the STEP\_PROG rule in § 3.5 which formalises a single step of the program are given below:

<sup>&</sup>lt;sup>4</sup> As outlined in § 3 and provided in full in [21].

We prove introduction and elimination lemmas in this way for all of the rules in the official BIL specification [6] with respect to our changes (§ 3). In total, the BIL\_specification locale consists of over 500 lemmas and rules.

# 4.2 The Program Locale

Recall that our workflow (Figure 1) proceeds by *Step 1*: compiling the given program; *Step 2*: feeding the resulting assembly into BAP to generate the corresponding BIL<sub>ADT</sub>; and *Step 3*: using IsaBIL to automatically generate an Isabelle/HOL locale for the given BIL<sub>ADT</sub> input. Note that if a binary is distributed without source code, then Step 1 could be skipped and the given assembly could be fed directly into BAP to generate the BIL<sub>ADT</sub>.

The locale for a program prog is generated using IsaBIL's translation tool, which is written in Isabelle/ML and is invoked using the custom Isabelle/HOL commands BIL or BIL\_file for inline or external BIL in BILADT format, respectively. Both commands take as an input, a name for the locale and either a BIL string (for BIL) or a filename (for BIL\_file). Within this locale, we automatically generate a decode predicate,  $\mapsto_{prog}$ , that maps each machine state  $(\Delta, pc, mem)$  to an instruction.

Note that, internally, Isabelle maintains the  $BIL_{ADT}$  format, however, we choose to represent it using class locales [50, 3, 41] to maintain human-readable syntax. For instance, without these syntax classes, expressing a direct jump to the fixed program address 3076 would require writing RAX := Val(Imm(Word(3076,64))). By instantiating the word syntax (nat :: sz, see Figure 3), we can simplify the expression to the syntax RAX := (3076 :: 64).

In addition to  $\mapsto_{\mathsf{prog}}$ , a program's locale defines  $Step\ 1$ : an  $address\ set$ ,  $\mathtt{addr\_set}: \mathbb{P}(word)$  (defining the set of addresses that have corresponding instructions) and  $Step\ 2$ : a  $symbol\ table$ ,  $\mathsf{sym\_table}: string \to word$  (mapping the binary's symbols, e.g. main, memcpy, free, as string literals to raw addresses).

Both addr\_set and sym\_table capture additional information about a binary that can be used later in a proof. For example, the addr\_set is useful for determining whether the program counter points to a valid address and is particularly important for validating the correctness of indirect jumps. Many binary proofs verify that execution from some entry point, such as the main function, is either correct or incorrect with respect to some property. Symbols typically represent entry points to functions and although the address of an entrypoint may differ between binaries, the symbol will remain constant. Hence, referring to positions within the binary using symbol names, stored in the sym\_table rather than program addresses, is often more convenient. Further details regarding the extraction of the addr\_set and sym\_table from a binary can be found in § 6.3.

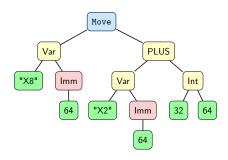

▶ Example 5. Consider the Binary\_A program below, written in BIL<sub>ADT</sub>, which corresponds to the BIL instruction X8 := X2 + 32. We assume the program has been compiled for RISC-V; for readability, BIL<sub>ADT</sub> provides the original assembly at Example 5. The program locale corresponding to Example 5 starts on Example 5, which fixes the corresponding decode predicate.

**Externally linked binaries.** Binaries often include links to external code, typically in the form of function calls. Accurately modeling these external calls is crucial for understanding the behavior of the original binary. IsaBIL provides two methods for handling externally linked code, depending on the availability of that external code. If the external binary is available, an Isabelle/HOL locale can be generated for the external binary, which is then combined with the existing binary locale through inheritance. If the external binary is not available, we can make assumptions about its behavior and define an approximate implementation using locale assumptions. We give an example for both cases in [21].

# 5 (In)correctness

In this section, we present the IsaBIL encoding of Hoare and Incorrectness logic (see Figure 2). Our locale-based encoding combines both into a single proof system **inference\_rules** locale, where we verify the AGREEMENT and DENIAL lemmas (see [42]).

Hoare and O'Hearn triples define (in)correctness of a command c over a pre-state  $\sigma$  satisfying the predicate P, resulting in a post-state  $\tau$  satisfying the predicate Q. In the locale, we assume the existence of a big-step transition relation  $(c, \sigma) \Rightarrow \tau$  defining the execution of c from state  $\sigma$  to termination, resulting in state  $\tau$ . Thus, we have the well-known under- and over-approximating rules:

$$\frac{(\text{HOARE})}{\forall \sigma, \tau. \ ((c, \sigma) \Rightarrow \tau) \implies (P(\sigma) \implies Q(\tau))}{\{P\}c\{Q\}} \qquad \frac{(\text{OHEARN})}{\forall \tau. \ Q(\tau) \implies \exists \sigma. \ P(\sigma) \land ((c, \sigma) \Rightarrow \tau)}{[P] \ c \ [Q]}$$

Note that our definition of correctness follows partial correctness, meaning termination is not guaranteed. We encode Hoare and Incorrectness triples as locales **correctness** =  $(\Rightarrow)$  and **incorrectness** =  $(\Rightarrow)$ , respectively, both of which are parameterised by  $\Rightarrow$ . Within the **correctness** locale, we verify standard Hoare logic rules, e.g.,

$$\frac{\text{(POST\_CONJ\_CORR)}}{\{P\}c\{Q_1\}} \quad \frac{\text{(PRE\_DISJ\_CORR)}}{\{P_1\}c\{Q\}} \quad \frac{\{P_1\}c\{Q\}}{\{P_1\}v\{Q\}} \quad \frac{\{P_2\}c\{Q\}}{\{P_1\}v\{Q\}} \quad \frac{P' \implies P \quad \{P\}c\{Q\} \quad Q \implies Q'}{\{P'\}c\{Q'\}}$$

Similarly, within the incorrectness locale, we verify rules for Incorrectness logic, e.g.,

We then combine these to form a locale **inference\_rules** =  $(\Rightarrow)$ , again parameterised by  $\Rightarrow$ . Within this combined locale, we are able to prove the AGREEMENT and DENIAL rules [42]:

$$\frac{(\text{AGREEMENT})}{[U] \, c \, [U']} \, \frac{U \implies O}{U' \implies O'} \, \frac{\{O\} c \{O'\}}{[U] \, c \, [U']} \, \frac{U \implies O}{U' \implies O'} \, \frac{[U] \, c \, [U']}{\neg (\{O\} c \{O'\})}$$

For proofs of incorrectness, it is typically not enough to simply state that if [P] c[Q] holds for an error state Q then the program c is incorrect. A program cannot be incorrect if there is no valid state that satisfies Q and as such, we must ensure that Q is non-trivial, i.e.,  $\exists \sigma. Q(\sigma)$ . Proving that Q is non-trivial can be difficult, as Q is often an over-approximation of the actual set of post-states (defined by some predicate Q') reachable from P. Therefore, proofs of incorrectness usually take the form  $\exists Q'. [P] c[Q'] \land (\forall \sigma. Q'(\sigma) \Longrightarrow Q(\sigma)) \land (\exists \sigma. Q'(\sigma))$ . Note that this does not necessarily imply that  $[P] c[Q] \land (\exists \sigma. Q(\sigma))$  since the implication is in the wrong direction to apply the STRENGTHEN\_WEAKEN\_INCORR rule.

# 6 Automation and Examples

In this section, we bring together the BIL\_specification and the inference\_rules locales to create a new locale, BIL\_inference (see § 6.1), providing a proof environment for BIL programs. This in turn enables us to develop a large number of highly reusable proof automation procedures for verifying both correctness and incorrectness of BIL programs (see § 6.2). The final major component of IsaBIL automation is the BIL<sub>ADT</sub> parser that automatically generates Isabelle/HOL locales for BIL programs (§ 6.3), providing a smooth and seamless pipeline from BAP to Isabelle/HOL proofs. We offer an overview of IsaBIL, discussing correctness and incorrectness proofs for a handful of examples.

#### **6.1** The BIL\_inference locale

BIL\_inference interfaces with the BIL\_specification and inference\_rules locales (see Figure 2) and is later extended with instances of state models (e.g., allocation and find\_symbol) to enable verification of generated BIL programs. Therefore, it is one of IsaBIL's most complex components.

Our first task is to define a big-step relation,  $\Longrightarrow_{BIL}$ , required by **inference\_rules**, using the BIL step relation,  $(\Delta, pc, mem) \leadsto (\Delta', pc', mem')$ , defined in § 3.5. One option for defining  $\Longrightarrow_{BIL}$  is to simply take the transitive closure of  $\leadsto$ . However, this would mean that the pre/postconditions that we define in our example would be predicates over the full variable store  $\Delta$ , which is heavy-handed.

An alternative (which is the approach we take) is to define another transition relation  $\xrightarrow{BIL}$  that abstracts  $\sim$ , and define  $\Longrightarrow$  as the transitive closure of  $\Longrightarrow$ . As we shall see, this vastly increases the flexibility of our approach, which becomes (1) extensible, since  $\Longrightarrow$  can be used to cover additional program features such as memory allocation (see § 6.4.1), and (2) more efficient since the components of  $\Delta$  that are not needed for the proof can be ignored. Thus, assuming  $\mathcal{C} = (\Delta, pc, mem)$ , we have:

$$(PROGRAM\_BIG\_STEP) \\ \mathcal{C} = (\_, pc, \_) \quad pc \in \texttt{addr\_set} \\ \mathcal{C} \rightsquigarrow \mathcal{C}' \quad (\mathcal{C}, \sigma) \xrightarrow[BIL]{} \tau \\ (\mathcal{C}, \sigma) \xrightarrow[BIL]{} \tau \\ (\mathcal{C}, \sigma) \xrightarrow[BIL]{} \tau \\ ((\mathcal{C}, \sigma) \xrightarrow[BIL]{} \tau \\ ((\mathcal{$$

Here, we assume addr\_set is the set of addresses that contain program instructions (see § 4.2), which will be later instantiated by a program's locale. A program may take a step as long as the current program counter corresponds to a program instruction. Note that the precise state model (i.e., type of  $\sigma$ ,  $\sigma'$  and  $\tau$ ) that one uses in PROGRAM\_BIG\_STEP and PROGRAM\_BIG\_STEP\_LAST will depend on the verification task at hand. If required, one could also take  $\sigma = \Delta$  allowing the proofs to inspect the full variable state (at a low level of abstraction).

Overall, we obtain a locale BIL\_inference =  $(\mapsto, \xrightarrow{BIL}, \text{addr\_set})$ . This locale extends the BIL\_specification (from §4) from which we inherit the decode predicate,  $\mapsto$ . Then, we use  $\xrightarrow{BIL}$  and addr\_set to define  $\xrightarrow{BIL}$  as above. This allows us to interpret the inference\_rules as sublocale, instantiating the parameter  $\Rightarrow$  to  $\xrightarrow{BIL}$ .

Within BIL\_inference, we can prove several rules of Hoare and Incorrectness logic in terms of the BIL semantics. These proofs are trivial at this level, but are nevertheless critical for proof automation since they can be used by all of our examples [21].

**Stuckness and Undefined Behaviour.** A BIL program is considered stuck if it reaches a state where no transition rules apply. Programs that become stuck are deemed correct, as they do not terminate.

The most common cause of stuckness in BIL is an attempt to decode an instruction at an address that does not exist within the program (see § 3.5). This typically occurs when a jump targets a non-existent address, resulting in a post-state with no valid instruction to execute. However, the big step semantics treat this as valid program termination rather than an explicit error. If the prover wishes to ensure that the program terminates with an expected PC they may assert its value in an (in)correctness triple's post-state Q.

Stuckness may also arise due to type errors, such as assigning a variable a value of an incompatible type. These types of stuckness are prevented by ensuring BIL statements are type correct, which can be achieved using IsaBIL's automated type checker (see [21]). In our proofs, we verify type correctness when necessary to prevent stuckness. More details, along with an example, can be found in the BIL manual [6].

Many traditional sources of stuckness in program semantics, such as dereferencing invalid memory or reading from uninitialized registers, result in undefined behaviour (UB) for BIL. In BIL, UB is represented using the **unknown**[str]: t value. For example, if an uninitialized register is used:

```

mv a6, a5 # UB if a5 was never initialized

```

Since the value of a5 (a 64 bit register) is unspecified,  $\mathbf{unknown}[str] : \mathbf{imm}\langle 64 \rangle$  will be set to a6. Evaluating BIL semantics that contain unknown values (such as a6 + 5) will propagate further unknowns unless avoided by control flow structures such as if-then-else. However, this does not necessarily lead to stuckness, except in cases where the target of a dynamic jump is unknown (i.e.  $\mathbf{jmp} \ \mathbf{unknown}[str] : \mathbf{imm}\langle 64 \rangle$ ). In such cases, the program cannot take a step as it does not know which program address to jump to. In (in)correctness logic, unknowns that do not lead to stuckness may still prevent the discharge of the post-state (Q). Unknown values in BIL can be resolved by explicitly specifying constraints on the program and pre-state as required.

#### 6.2 Proof Automation

Instruction set architectures (ISAs), despite their large scale, are inherently finite, and compilers employ common patterns for optimization. Additionally, developers leverage reusable components such as *functions* and *gadgets* to perform common tasks. Consequently,

binaries often exhibit a significant degree of repetition. Once identified, this repetition can be verified without the need for human input. IsaBIL exploits this repetition to alleviate the burden associated with proof construction and verification. In this section, we outline the proof automation techniques employed by IsaBIL.

#### 6.2.1 Eisbach

IsaBIL heavily leverages Eisbach [33], an Isabelle tactic framework for proof automation, to discharge proof goals automatically. We create Eisbach methods for symbolic execution (sexc) and type checking (typec) which utilise IsaBIL's introduction and elimination rules to solve both big- and small-step BIL statements, expressions and variables as well as proving type correctness. These methods employ a best-effort approach. If a case that cannot be solved automatically occurs, the methods will backtrack to a safe state and the partially completed proof context will be handed back to the human prover, whereby corrections or manual inputs can be made before resuming the automation (see [21] for details).

# 6.2.2 Human Readability

In assembly languages, registers are typically assigned specific names and types. However, in BIL, registers are represented as generic variables of type var. These variables are parameterised with names and types. For example, the RISC-V registers R0-31 are represented by the variables ("R0-31":  $imm\langle 64\rangle$ ). While this representation offers flexibility, it can be verbose. It is common knowledge for RISC-V developers that R0-31 are registers capable of storing 64-bit words. To enhance program readability, we define the set of registers for riscv64 [55] as the 64-bit registers R0-31:  $imm\langle 64\rangle$ . Additionally, we introduce syntax abbreviations for the 64-bit x86 architecture.

# 6.2.3 Architecture-Specific Proof Optimisations (for RISC-V)

Whilst IsaBIL provides sufficient granularity to handle many architectures out of the box, the speed and efficiency of proofs can be improved by tailoring optimizations to specific hardware architectures. This section describes the proof optimizations undertaken for RISC-V.

**Instructions.** Modern architectures comprise of large instruction sets. Proofs of programs can be optimised by verifying high-level lemmas corresponding to program steps of the most commonly used instructions directly in the BIL\_inference locale. For example, IsaBIL provides step rules for the 32-bit (4-byte) RISC-V instructions auipc, jalr and ld.

```

auipc \ rd, \ imm = \{ addr = pc, size = 4 :: 64, code = \{ rd := pc + imm \} \}

```

The auipc (Add Upper Immediate to Program Counter) instruction facilitates the computation of an absolute address. It achieves this by adding the immediate value imm to pc, storing the result in the destination register rd. auipc is commonly used to create jump targets, such as those for external functions.

```

\texttt{jalr}\ rd,\ rs1,\ of\!fset = \{ \ \mathbf{addr} = pc, \mathbf{size} = 4 :: 64, \mathbf{code} = \{ rd := pc + 4;\ \mathbf{jmp}\ rs1 + of\!fset \} \ \}

```

The jalr (Jump And Link Register) instruction performs an unconditional jump. It sets pc to the address stored in the source register rs1 with an optional immediate value offset. The address of the subsequent instruction is then stored in the destination register rd. This instruction is used for function calls, where it is important to preserve the return address.

```

1d rd, offset(rs1) = \{ addr = pc, size = 4 :: 64, code = \{ rd := mem[rs1 + offset, el] : 64 \} \}

```

```

00000000000104a0 <malloc@plt>:

104a0: 00002e17

auipc

t3,0x2

t3,-1160(t3) # 12018 <malloc@GLIBC_2

104a4: b78e3e03

ld

.27>

104a8: 000e0367

jalr

t1.t3

104ac: 00000013

nop

0000000000104b0 <free@plt>:

104b0: 00002e17

auipc

t3,0x2

104b4: b70e3e03

ld

t3,-1168(t3) # 12020 <free@GLIBC_2

27>

104b8: 000e0367

jalr

t1.t3

10

104bc: 00000013

11

```

#### **Figure 5** PLT stubs for free and malloc.

The 1d (Load Double) instruction is used to load a 64-bit word, referred to as a double word, from memory. First, 1d computes an address by adding the contents of the source register rs1 to the immediate *offset*. The value at this address in memory is then stored in the destination register rd. 1d is the primary means of retrieving data of this size from memory.

Representing the instructions auipc, jalr and ld as the high-level program step lemmas (given below) allows the prover to otherwise skip the lengthy reduction for a program step. The rules for these instructions are provided below:

```

\begin{array}{l} \text{(AUIPC\_LEMMA)} \\ \hline (\Delta, pc, mem) \mapsto \texttt{auipc}\ rd,\ imm \\ \hline (\Delta, pc, mem) \leadsto (\Delta(rd \mapsto pc + imm), pc + 4), mem) \end{array} \\ \hline \begin{array}{l} \text{($\Delta, pc, mem)} \mapsto \texttt{jalr}\ rd,\ rs1,\ offset\ (rs1, addr) \in \Delta} \\ \hline (\Delta, pc, mem) \mapsto \texttt{jalr}\ rd,\ rs1,\ offset\ (rs1, addr) \in \Delta} \\ \hline \text{($\Delta, pc, mem)} \mapsto \texttt{jalr}\ rd,\ rs1,\ offset\ (rs1, addr) \in \Delta} \\ \hline \\ \text{($\Delta, pc, mem)} \mapsto \texttt{jalr}\ rd,\ rs1,\ offset\ (rs1, addr) \in \Delta} \\ \hline \text{($\Delta, pc, mem)} \mapsto \texttt{jalr}\ rd,\ rs1,\ offset\ (rs1, addr) \in \Delta} \\ \hline \\ \text{($\Delta, pc, mem)} \mapsto \texttt{jalr}\ rd,\ rs1,\ offset\ (rs1, addr) \in \Delta} \\ \hline \text{($\Delta, pc, mem)} \mapsto \texttt{jalr}\ rd,\ rs1,\ offset\ (rs1, addr) \in \Delta} \\ \hline \\ \text{($\Delta, pc, mem)} \mapsto \texttt{jalr}\ rd,\ rs1,\ offset\ (rs1, addr) \in \Delta} \\ \hline \text{($\Delta, pc, mem)} \mapsto \texttt{jalr}\ rd,\ rs1,\ offset\ (rs1, addr) \in \Delta} \\ \hline \text{($\Delta, pc, mem)} \mapsto \texttt{jalr}\ rd,\ rs1,\ offset\ (rs1, addr) \in \Delta} \\ \hline \text{($\Delta, pc, mem)} \mapsto \texttt{jalr}\ rd,\ rs1,\ offset\ (rs1, addr) \in \Delta} \\ \hline \text{($\Delta, pc, mem)} \mapsto \texttt{jalr}\ rd,\ rs1,\ offset\ (rs1, addr) \in \Delta} \\ \hline \text{($\Delta, pc, mem)} \mapsto \texttt{jalr}\ rd,\ rs1,\ offset\ (rs1, addr) \in \Delta} \\ \hline \text{($\Delta, pc, mem)} \mapsto \texttt{jalr}\ rd,\ rs1,\ offset\ (rs1, addr) \in \Delta} \\ \hline \text{($\Delta, pc, mem)} \mapsto \texttt{jalr}\ rd,\ rs1,\ offset\ (rs1, addr) \in \Delta} \\ \hline \text{($\Delta, pc, mem)} \mapsto \texttt{jalr}\ rd,\ rs1,\ offset\ (rs1, addr) \in \Delta} \\ \hline \text{($\Delta, pc, mem)} \mapsto \texttt{jalr}\ rd,\ rs1,\ offset\ (rs1, addr) \in \Delta} \\ \hline \text{($\Delta, pc, mem)} \mapsto \texttt{jalr}\ rd,\ rs1,\ offset\ (rs1, addr) \in \Delta} \\ \hline \text{($\Delta, pc, mem)} \mapsto \texttt{jalr}\ rd,\ rs1,\ offset\ (rs1, addr) \in \Delta} \\ \hline \text{($\Delta, pc, mem)} \mapsto \texttt{jalr}\ rd,\ rs1,\ offset\ (rs1, addr) \in \Delta} \\ \hline \text{($\Delta, pc, mem)} \mapsto \texttt{jalr}\ rd,\ rs1,\ offset\ (rs1, addr) \in \Delta} \\ \hline \text{($\Delta, pc, mem)} \mapsto \texttt{jalr}\ rd,\ rs1,\ offset\ (rs1, addr) \in \Delta} \\ \hline \text{($\Delta, pc, mem)} \mapsto \texttt{jalr}\ rd,\ rs1,\ offset\ (rs1, addr) \in \Delta} \\ \hline \text{($\Delta, pc, mem)} \mapsto \texttt{jalr}\ rd,\ rs1,\ offset\ (rs1, addr) \in \Delta} \\ \hline \text{($\Delta, pc, mem)} \mapsto \texttt{jalr}\ rd,\ rs1,\ rs1,\ offset\ (rs1, addr) \in \Delta} \\ \hline \text{($\Delta, pc, mem)} \mapsto \texttt{jalr}\ rd,\ rs1,\ rs1,\

```

Further semantics for addi, sd and ret RISC-V instructions are provided in [21].

**Execution.** We also prove high-level big-step semantics rules for common gadgets in binary executables. For example, the *procedure linkage table* (PLT) acts as an intermediary between the current program and shared libraries, including C's standard library. The PLT facilitates indirect calls to external functions, whose locations are unknown until runtime when they are resolved by the dynamic loader. In the dump of the RISC-V binary for Listing 1 given in § 6.2.3, we can observe the presence of stubs within the PLT, representing entries for each external call. Specifically, in § 6.2.3, the stubs correspond to the functions free and malloc that are called by the program.

By leveraging the consistent pattern observed in PLT entries, we can construct universal big-step rules for PLT stubs, as demonstrated below.

```

\begin{array}{c} (\text{PLT\_STUB\_LEMMA}) \\ (\Delta_1, pc, mem) \mapsto \text{auipc } t3, \ 0x2 \qquad (\Delta_2, pc+4, mem) \mapsto \text{1d } t3, \ offset(t3) \\ (\Delta_3, pc+8, mem) \mapsto \text{jalr } t1, \ t3, \ 0 \qquad \{pc, pc+4, pc+8\} \subseteq \text{addr\_set} \\ \Delta_2 = \Delta_1(t3 \mapsto pc+0x2) \qquad \Delta_3 = \Delta_2(t3 \mapsto w) \qquad \Delta_4 = \Delta_3(t1 \mapsto pc+12) \\ ((\Delta_1, pc, mem), \sigma_1) \xrightarrow{BIL} \sigma_2 \qquad ((\Delta_2, pc+4, mem), \sigma_2) \xrightarrow{BIL} \sigma_3 \qquad ((\Delta_3, pc+8, mem), \sigma_3) \xrightarrow{BIL} \sigma_4 \\ ((\Delta_4, w, mem), \sigma_4) \xrightarrow{BIL} \tau \qquad (mem, v) \in \Delta_1 \qquad \Delta \vdash v[pc+0x2+offset, \mathbf{el}] : 64 \sim^* w \\ \hline \\ ((\Delta_1, pc, mem), \sigma_1) \xrightarrow{BIL} \tau \\ \end{array}

```

Now, if we encounter a PLT stub in a proof at a lower level, we can discharge the proof obligation efficiently using PLT\_STUB\_LEMMA. This lemma significantly reduces the proof effort required. Without PLT\_STUB\_LEMMA, one must apply over 150 rules to achieve the same result. Furthermore, by applying this approach to stack allocations and deallocations, we eliminate the need for approximately 50 rules in the case of allocation and 250 rules in the case of deallocation. Further details on this are provided in [21].

#### 6.3 BIL to ISABIL transpiler

A key component of our IsaBIL framework is a verified BIL parser that transpiles BIL<sub>ADT</sub> programs into an Isabelle/HOL locale to enable verification.

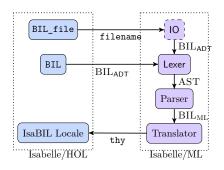

Parsing occurs in two distinct phases. The first phase involves the translation of  $BIL_{ADT}$  into  $BIL_{ML}$ , a format suitable for manipulation within Isabelle/ML. This intermediate step enables analysis tasks in Isabelle/ML, such as calculating the size of instructions. The second phase involves translating  $BIL_{ML}$  into an Isabelle/HOL representation, which is the starting point for verification. Parsing can be invoked directly on a  $BIL_{ADT}$  string with BIL or alternately on a file containing  $BIL_{ADT}$  with  $BIL_{file}$ . An overview of the parsing process is given in Figure 6.

During the first phase, the parser iterates over the instructions in a BIL<sub>ADT</sub> input. It captures and stores all program addresses in addr\_set. Moreover, the parser associates symbols with a program address in sym\_table. Since the syntax of BIL<sub>ADT</sub> resembles a tree structure, it is intuitive to convert it into an Abstract Syntax Tree (AST) using a lexer. This AST is processed by a Recursive Descent Parser (RDP), which traverses each node in the tree depth-first, matching the node's value to a corresponding parsing function. For example, if the parser encounters a Var node, it will attempt to parse the first child as a string and the second child as a BIL type. This process transforms the input into BIL<sub>ML</sub>, a structured data type closely resembling BIL<sub>ADT</sub> which can be manipulated within Isabelle/ML.

The second phase defines a locale within the current proof context with a fixed decode predicate. For each BIL<sub>ML</sub> instruction, an assumption is added to the locale, stating how a program with any variable state and memory, but with the instructions program address, decodes to an Isabelle/HOL representation of said instruction. To obtain the Isabelle/HOL representation, an RDP translator recursively converts each BIL<sub>ML</sub> instruction to Isabelle/HOL terms defined in the BIL\_specification locale (see § 4).

The first phase of the parser harnesses Isabelle/HOL's code generation, where specifications for both the lexer and parser were defined within Isabelle/HOL and subsequently translated into ML. BIL<sub>ML</sub> for example, is a direct ML representation of the BIL specification from the IsaBIL framework. Using code reflection, we import the generated ML code back into Isabelle/HOL as a plugin. Consequently, the lexer and parser are formally verified under the Isabelle/HOL framework. In contrast, the second phase employs non-code-generated ML. This decision stems from its necessity to interface with Isabelle/HOL's core ML library, which cannot be achieved via code-generated ML. To bridge this gap, we introduce a minimal layer of unverified ML code that lifts the BIL representation obtained from the verified parser into Isabelle/HOL's proof system. Below, as an example, we present a snippet of the translation code responsible for converting BIL<sub>ML</sub>'s binary operations to IsaBIL's binary operations:

```

n mk_exp (AstParser.BinOp (e1,bop,e2)) = @{term "BinOp"} $ mk_exp e1 $

mk_bop bop $ mk_exp e2

```

Note that Isabelle isolates Isabelle/ML programming, and hence our parser cannot interfere with the soundness of Isabelle's core logic engine.

Figure 6 Overview of the BIL parser, entrypoints via the BIL or BIL\_file commands.

Figure 7 AST representation of the BIL<sub>ADT</sub> statement Move(Var("X8", Imm(64)), PLUS(Var("X2", Imm(64)), Int(32, 64))).

**Table 2** Overview of theories and lemma **Table 3** AV rules with description. for each of IsaBIL's components.

| Component                               | Lemmas |

|-----------------------------------------|--------|

| Correctness                             | 13     |

| Incorrectness                           | 3      |

| Inference Rules                         | 2      |

| BIL Specification (including syntax)    | 594    |

| BIL Inference                           | 13     |

| RISC-V optimisations                    | 74     |

| Alloc Model                             | 6      |

| Find Symbol                             | 0      |

| Double Free (total for both examples)   | 77     |

| AV Rules (total for all seven examples) | 187    |

| AVR | Description (the following shall not be used)                           |

|-----|-------------------------------------------------------------------------|

| 17  | The error indicator errno                                               |

| 19  | <pre><locale.h> and the setlocale function<sup>5</sup></locale.h></pre> |

| 20  | The setjmp macro and the longjmp functions                              |

| 21  | The signal handling facilities of <signal.h></signal.h>                 |

| 23  | The library functions atof, atoi and atol from lib-                     |

|     | rary <stdlib.h></stdlib.h>                                              |

| 24  | The library functions abort, exit, getenv and system                    |

|     | from library <stdlib.h></stdlib.h>                                      |

| 25  | The time handling functions of library <time.h></time.h>                |

#### 6.4 **Example Proofs**

The majority of the development consists of general tactics and lemmas which can be reused across multiple developments. We give the number of lemmas for each component in Table 2.

All of the sublocales and inherited locales can reuse the proofs of the higher-level (more abstract) locales. Thus, for instance, the 594 lemmas of the BIL\_specification locale are applicable to BIL\_inference and all of the examples, which improves re-usability. The RISC-V optimisations help improve performance and are reusable across all examples. The theories for double\_free\_\* and find\_symbol are general and apply to all corresponding examples. Finally, each example comprises a step lemma for each line of code. Using the earlier optimisations, solving them is trivial and only requires running the automated tactics.

To motivate IsaBIL, we employ a combination of correctness and incorrectness proofs, focusing on illustrative examples frequently referenced in BAP literature [8]. These examples represent patterns commonly found within much larger programs/libraries.

#### **Double Free** 6.4.1

We detail the (in)correctness proofs for CWE-415: Double Free outlined in §2. To classify this vulnerability, we require a memory allocation model, which is not part of the BIL semantics (§ 3). Memory allocation in C is reflected as a PLT stub in the binary. In particular, we are only required to track the pointer (memory address) that is allocated (and later freed). To this end, we develop a locale, allocation, that extends the BIL semantics (see Figure 2) with an abstract allocation model inspired by earlier works [34, 31].

$$(ALLOC)$$

$$is\_alloc(C) \quad w = next\_ptr(\omega_A)$$

$$sz = get\_sz(C)$$

$$\omega'_A = \omega_A.[alloc(w, sz)]$$

$$(C, \omega_A) \xrightarrow{A} \omega'_A$$

$$(FREE)$$

$$is\_free(C) \quad w = get\_ptr(C)$$

$$\omega'_A = \omega_A.[free(w)]$$

$$(C, \omega_A) \xrightarrow{A} \omega'_A$$

$$(C, \omega_A) \xrightarrow{A} \omega'_A$$

$$(SKIP)$$

$$\neg is\_free(C)$$

$$\neg is\_alloc(C)$$

$$(C, \omega_A) \xrightarrow{A} \omega'_A$$

Figure 8 Allocation semantics.

The allocation locale. We define allocation by instantiating the small-step transition relation  $\xrightarrow{BIL}$  of BIL\_specification (see §6.1). We start by defining two memory operations:

```

memop ::= alloc(w, sz) \mid free(w)

```

where w is the memory being allocated or freed and sz is the size. Additionally, we assume an abstract allocation function next\_ptr :  $memop^* \rightarrow word$  that serves the purpose of selecting suitable memory addresses for allocation and retrieves the next address from the allocator based on the given history (sequence) of allocations and deallocations. For each allocation, we use next\_ptr to obtain the next available memory address. Consequently, in the state of allocation, we must track the sequence of memop operations, which is provided to next\_ptr as an input whenever an allocation occurs. For the Double Free example, no other variables need to be tracked, hence we simply assume the state to be this sequence, which we denote  $\omega_A : memop^*$ .

Recall that by using the  $\mapsto$  predicate (§ 3.5), the BIL instruction corresponding to  $\mathcal{C} = (\Delta, pc, mem)$  can be uniquely identified. We use predicates is free:  $proq \to bool$  and is\_alloc:  $prog \rightarrow bool$ , which hold when the next instruction to be executed in the given  $\mathcal{C} \in prog$  corresponds to a free and allocation instruction, respectively. We assume that an instruction that frees memory cannot simultaneously perform an allocation and vice versa, i.e.,  $\neg is\_free(C) \lor \neg is\_alloc(C)$ . When the instruction for C is an allocation, we utilise the function get  $sz: prog \rightarrow sz$  to obtain the size allocated and when the instruction for  $\mathcal{C}$  is a deallocation, we utilise the function  $\mathtt{get\_ptr}: prog \to word$  to obtain the address that is freed. The size and location can be determined using the  $\mapsto$  function on the given  $\mathcal{C}$ . Thus, we define a small-step transition relation,  $\xrightarrow{\mathcal{A}}$ , over allocations in Figure 8.

We encode this allocation model as the locale allocation, fixing the functions next\_ptr, is\_free, is\_alloc, get\_sz and get\_ptr. This locale is derived as an interpretation of the locale BIL\_inference retaining the decode predicate  $\mapsto$  and address set addr\_set as abstract, but overriding  $\xrightarrow{BIL} = \xrightarrow{\mathcal{A}}$ . Thus, we have the signature **allocation** =  $(\mapsto,$ addr\_set,next\_ptr, is\_free,is\_alloc,get\_sz,get\_ptr), where parameters next\_ptr, is\_free, is\_alloc, get\_sz and get\_ptr are used to derive  $\xrightarrow{\Lambda}$  within the locale.

The double\_free\_bad and double\_free\_good locales. These locales correspond to the double free program and are auto-generated from the corresponding BIL programs (shown in Listings 3 and 4). This step is trivial when using ISABIL's BIL file command, which we have developed using Isabelle/ML. In particular, we invoke the Isabelle/HOL commands:

```

BIL_file <double-free-bad.bil.adt> defining double_free_bad

BIL_file <double-free-good.bil.adt> defining double_free_good

```

where double-free-bad.bil.adt is a file containing the BIL for Listing 1 in BILADT format and double\_free\_bad is the name of the locale to be generated. The good version is similar. The double\_free\_\*\_proof locales. We combine the locales generated from the BIL programs with our allocator locale (allocation) to produce new locales double\_free\_bad\_proof and double\_free\_good\_proof. Recall from § 4.2 that for each locale generated from a BIL\_ADT program, we have access to a symbol table sym\_table mapping strings (i.e., external function calls) to the program address at which the symbol appears. Note that when a BIL program calls a function, it typically stores the return address, then jumps to the function. The symbol corresponding to the program counter after the jump contains the name of the external function, which is stored in the symbol table. In RISC-V convention, the first argument of a function call is stored in the register X10. To allocate memory, function malloc is called with the size as the first argument whereas to deallocate a pointer, function free is called with the pointer as the first argument. Therefore, we can obtain the size allocated by a call to malloc and pointer freed by a call to free by retrieving the value stored in register X10.

We therefore instantiate the predicates is\_free, is\_alloc, get\_sz and get\_ptr from the allocation locale as follows:

The exact implementation of next\_free occurs at a lower level of abstraction, and depends on the allocation model. At this level, we provide the main requirement axiomatically, i.e., we require

$$w = \mathtt{next\_ptr}(\omega_{\mathcal{A}}) \implies (\forall i. \ \omega_{\mathcal{A}}(i) = \mathtt{alloc}(w, sz) \implies \exists j. \ j > i \land \omega_{\mathcal{A}}(i) = \mathtt{free}(w))$$

This presents us with all the components necessary to prove (in)correctness of our examples. The following predicate captures the double-free over the memory state defined above:

$$\begin{split} \texttt{double\_free\_vuln} = \lambda \omega_{\mathcal{A}}. \ \exists i, j, w. \ i < j \wedge \omega_{\mathcal{A}}[i] = \texttt{free}(w) \wedge \omega_{\mathcal{A}}[j] = \texttt{free}(w) \wedge \\ (\forall k. \ i < k < j \implies \omega_{\mathcal{A}}[k] \neq \texttt{alloc}(w, sz)) \end{split}$$

Note that the predicate captures *only* the double-free vulnerability and does not formalise other pointer misuse vulnerabilities, e.g., use-after-free or free-before-alloc.

▶ Theorem 6. Let  $C_{bad}$  and  $C_{good}$  be the programs corresponding to double\_free\_bad and double\_free\_good, respectively. Both of the following hold

```

1. \exists Q. [\neg double\_free\_vuln] C_{bad} [Q] \land (\forall \sigma. Q(\sigma) \Longrightarrow double\_free\_vuln(\sigma)) \land (\exists \sigma. Q(\sigma))

```

2.  $\{\neg double\_free\_vuln\}$   $C_{good}$   $\{\neg double\_free\_vuln\}$

Note that in  $C_{bad}$ , the memory error does not lead to early termination via the allocation semantics in Figure 8. The program continues executing as normal, but generates a history that can be shown to contain a double-free vulnerability at termination.

# **6.4.2 AV** rules

In a similar manner, we prove incorrectness of the AV rules from Table 3. Details of these proofs are provided in [21].

# 7 Case Study: Double-Free Vulnerability in cURL (CVE-2016-8619)

cURL is an open-source library primarily used for transferring data over the internet using various protocols, including TLS. It has a large user base, supporting multiple operating systems and architectures (including RISC-V), and thus ensuring the security of cURL is critically important.

```

static __attribute__ ((noinline)) CURLcode read_data(struct connectdata *conn,

curl_socket_t fd,

struct krb5buffer *buf)

{

int len;

void* tmp = NULL;

6

CURLcode result;

result = socket_read(fd, &len, sizeof(len)); // result = 0 iff socket_read successful

if (result)

if (len) {

len = ntohl(len);

tmp = realloc(buf->data, len);

len = ntohl(len):

tmp = realloc(buf->data, len);

16

if(tmp == NULL)

return CURLE_OUT_OF_MEMORY;

buf->data = tmp;

19

result = socket_read(fd, buf->data, len);

20

if(result)

turn result;

buf->size = conn->mech->decode(conn->app_data, buf->data, len,

23

conn->data_prot, conn);

25

buf \rightarrow index = 0:

return CURLE_OK;

26

```

Figure 9 The read\_data function of the cURL library in security.c. The snippet highlighted in red shows the vulnerable code in version 7.50.3, and that in green shows the corrected vulnerability in version 7.51.0.