# Sufficient Conditions for Robustness of RDMA Programs

Guillaume Ambal<sup>1</sup>, Ori Lahav<sup>2</sup>, and Azalea Raad<sup>1</sup>

Abstract. Remote Direct Memory Access (RDMA) is a modern technology enabling high-performance inter-node communication. Despite its widespread adoption, theoretical understanding of permissible behaviours remains limited, as RDMA follows a very weak memory model. This paper addresses the challenge of establishing sufficient conditions for RDMA robustness. We introduce a set of straightforward criteria that, when met, guarantee sequential consistency and mitigate potential issues arising from weak memory behaviours in RDMA applications. Notably, when restricted to a tree topology, these conditions become even more relaxed, significantly reducing the need for synchronisation primitives. This work provides developers with practical guidelines to ensure the reliability and correctness of their RDMA-based systems.

**Keywords:** RDMA · Robustness · Weak Memory Models

# 1 Introduction

Remote Direct Memory Access (RDMA) is a modern technology that enables a machine to have direct read/write access to the memory of another machine over a network, bypassing the operating systems on both ends. This allows such direct memory accesses (reads/writes) to be performed with far fewer CPU cycles, leading to high-throughput, low-latency networking, which is especially useful in massively parallel computer clusters (e.g. data centres). RDMA has achieved widespread adoption as of 2018 [68], thanks to efficient implementations available at comparable cost to traditional infrastructures (e.g. TCP/IP sockets) [31], with several RDMA technologies such as InfiniBand and RDMA over Converged Ethernet (RoCE) readily available.

RDMA networks directly interact with the hardware through read (get) and write (put) operations on remote memory. As a result, programming RDMA systems is conceptually similar to shared memory systems of existing hardware architectures (e.g. Intel-x86 or ARM). A key difference, however, is that on encountering a remote operation, the CPU forwards it onto the *network interface card* (NIC), which subsequently handles the remote operation without further CPU involvement.

The performance gains of RDMA, as well as its wide range of implementations, have led to a surge of RDMA research [4,72,70,26]. RDMA networks exhibit different degrees of concurrency, depending on whether the concurrent threads reside on different nodes (machines) over the network (inter-node concurrency) or on the same node (intra-thread concurrency). To understand the behaviour of RDMA programs and their various notions of concurrency, Ambal et al. [10] recently developed RDMA<sup>TSO</sup>, a formal semantics of RDMA programs where each node comprises an Intel-x86 CPU and thus intra-node-inter-thread concurrency is governed by the TSO (total store ordering) model [67].

As the real power of RDMA networks is their ability to run parallel programs over different nodes, writing efficient RDMA programs hinges on utilising internode concurrency. However, writing such programs correctly is far from straightforward. A key challenge is that local operations (accessing the local memory of the executing node) are handled by the CPU, while remote operations (accessing remote memory on other nodes) are handled by the NIC independently and in parallel to CPU operations. Hence, operations in the same thread may not be executed in the intended (program) order, leading to surprising outcomes. As Ambal et al. [10] note, this can result in counter-intuitive behaviours even in the case of sequential programs comprising a single thread. This is in stark contrast to all previously existing concurrency models (be they of CPU architectures or programming languages), where sequential programs do behave sequentially.

The permissive nature of RDMA semantics requires developers to carefully consider potential instruction reorderings. Reasoning about concurrent programs and ensuring proper synchronisation between threads is inherently complex, even without instruction reordering. Accounting for instruction reorderings adds another layer of complexity to this challenge.

As such, we should ideally enable reasoning about RDMA programs under a simpler, more intuitive model such as sequential consistency (SC) [42], where no instruction reordering is allowed, and thus instructions in each thread always execute in order. To this end, a common approach to simplify reasoning is to ensure robustness. A program P is robust under a consistency model CM, if its set of possible behaviours under CM coincide with those of its behaviours under SC; i.e. P is robust under CM if it exhibits no non-SC behaviours. If a program is robust under CM, then we can simply reason about it under SC, without considering the complexities of CM.

Contributions. In this paper, we close this gap and simplify reasoning about RDMA program through robustness. To simplify our presentation and not distract the reader from the RDMA complexities by the *orthogonal* intricacies of CPU concurrency, we first present RDMA<sup>SC</sup>, a simplification of the RDMA<sup>TSO</sup> model of Ambal et al. [10], where intra-node concurrency follows the simpler SC model [42], while inter-node concurrency is analogous to that of RDMA<sup>TSO</sup>. We then identify two sets of sufficient constraints that, if satisfied, ensure the robustness of RDMA<sup>SC</sup> programs. Our proposed constraints are purely *syntactic*, in that they do not require an understanding of the complex RDMA semantics and can be established by simply checking the syntax of the program. The first

set of constraints is restrictive, but can be applied to any RDMA program. The second relaxes the requirements of the first, but requires the RDMA network to follow a tree topology. Our conditions enable a number of useful paradigms for RDMA programs such as the server-client model, which we show can be used for automatically translating existing concurrent algorithms to distributed ones over RDMA, as well as for modelling star network topologies used e.g. in Local Area Networks (LAN). Finally, we adapt our results to the RDMA<sup>TSO</sup> model and accordingly propose analogous syntactic and topological constraints.

Outline. In §2 we present an intuitive account of the weak RDMA semantics through examples and discuss how we ensure robustness through syntactic constraints. In §3 we present our formal RDMA<sup>SC</sup> model. In §4 we establish sufficient syntactic conditions that ensure the robustness of RDMA<sup>SC</sup> programs. In §5 we apply these findings to tree-shaped network topologies, offering a further streamlined set of conditions under RDMA<sup>SC</sup>. We discuss related work in §6. The appendix contains the proofs of all theorems stated in this paper (§A), as well as the extension of all our results to the RDMA<sup>TSO</sup> model (§B).

# 2 Overview

We present an intuitive account of RDMA semantics through several examples, showing the counter-intuitive and unexpected behaviours they can exhibit due to possible *instruction reorderings* (§2.1). We then discuss how we can tame this complexity by introducing *syntactic constraints* that, if fulfilled, prohibit problematic instruction reorderings, pre-empting unexpected behaviours and thus simplifying the task of reasoning about RDMA programs for developers (§2.2).

### 2.1 RDMA Semantics at a Glance

Consistency (Concurrency) Models and Weak Behaviours. In the literature of shared-memory concurrent (multi-threaded) programming, the set of possible behaviours (i.e. semantics) of a concurrent program is defined via a consistency model (a.k.a. memory model or concurrency model), with a number of such models available in different domains such as hardware architectures (e.g. Intel and ARM) and programming languages (e.g. C/C++ and Java). The most well-known and intuitive consistency model is sequential consistency (SC, a.k.a. interleaving concurrency) [42], where the instructions are interleaved in program order. That is, under SC the instructions in each thread cannot be reordered. While simple, SC is too strong in that it precludes many common hardware/compiler optimisations and thus unduly hinders performance. As such, modern hardware architectures and programming languages adhere to weaker, more lenient models, admitting more behaviours than SC. In this context a program behaviour (outcome) is referred to as weak, if it is not allowed under SC. Such weak behaviours can typically be understood in terms of instruction reorderings within a thread or visibility delays (where the effects of an instruction (e.g. a write) is not observed at the same time by all threads), both of which are disallowed under SC.

4

Conceptual RDMA Model. We model concurrent RDMA programs running over a network of nodes (i.e. computers), where each node hosts zero, one, or more threads, and each thread can directly access remote memory of other nodes through its network interface card (NIC). As we discuss below, RDMA programs exhibit three sources of weak behaviours: 1. CPU weak behaviours, due to the usual interactions (and reordering) of multiple threads on a single node; 2. intra-thread weak behaviours, due to RDMA operations being reordered or delayed; and 3. inter-node weak behaviours, due to multiple nodes executing concurrently. Here we focus on the latter two sources as they are specific to RDMA programs, and discuss how such weak behaviours may be prevented.

CPU Concurrency. RDMA enacts data transfers between nodes via the NIC subsystems of the constituent nodes, which are independent from the CPU subsystems. Consequently, the RDMA technology can be combined with different CPU architectures governed by different memory models (e.g. TSO or ARM). The first validated formal model of RDMA programs, RDMA<sup>TSO</sup> [10], assumes that CPU concurrency is governed by the TSO model [67]. To simplify our presentation and not distract the reader from the RDMA complexities by the *orthogonal* intricacies of CPU concurrency, we present the simpler RDMA<sup>SC</sup> model, where CPU concurrency follow the stronger SC model [42]. We later generalise our results to RDMA<sup>TSO</sup> in the appendix (§B).

Almost all weak behaviours introduced by RDMA stem from the NIC and are independent of CPU concurrency (i.e. CPU and RDMA concurrency can often be decoupled). As such, the distinction between RDMA<sup>TSO</sup> and RDMA<sup>SC</sup> is often irrelevant, in which case we write RDMA\* to encompass both models. In particular, in this overview section we focus on nodes with *at most one thread each*, i.e. with no CPU concurrency, so all behaviours discussed below hold of both RDMA<sup>SC</sup> and RDMA<sup>TSO</sup> (i.e. for RDMA\*). Note that this is *merely a presentational choice* we have made in this section, and our formal models, theorems, and examples in subsequent sections also account for CPU concurrency.

**Litmus Test Outcome Notation.** We frequently present small representative examples (known as litmus tests in the literature). In each example, the outcomes annotated with  $\checkmark$  are allowed by the RDMA model under discussion, while those annotated with  $\checkmark$  are disallowed.

Remote Direct Memory Access (RDMA). RDMA programs comprise operations that access remote memory, as well as various synchronisation operations. As such, programming RDMA networks is conceptually similar to shared memory systems. To distinguish remote (RDMA) operations from CPU ones, we refer to RDMA reads and writes as get and put operations, respectively. To distinguish local and remote memory locations, we assume nodes do not reuse location names, we write  $x^n$  for a location on a remote node n, and write x for a location on the local node. A put operation is of the form  $x^n := y$  and consists of reading from a local location y and writing to a remote location x on x. Similarly, a get operation is of the form  $x := y^n$  and consists of reading from a remote location y on y and writing to a local location y. We write  $\overline{n}$  to identify

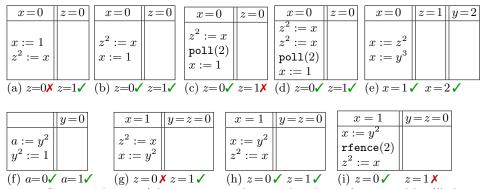

Fig. 1: Sequential RDMA\* litmus tests, where each column (separated by ||) denotes a distinct node, the statement on the top line of each column denotes the initial values of locations.

a node other than n. When node n issues a remote operation to be executed on node  $\overline{n}$ , we state that the operation is by n towards  $\overline{n}$ .

**Sequential (Single-Threaded) RDMA\* Behaviours.** When a thread issues a get or put operation, it is handled by the NIC, in contrast to local reads and writes handled by the CPU. As such, the interaction between CPU and remote operations lead to further behaviours even within a *sequential* (single-threaded) program. We demonstrate this in the examples of Fig. 1, where each column represents a distinct node, numbered from left to right starting from 1. For instance, the example in Fig. 1a comprises a single thread on node 1 (the leftmost column) that writes to the local location x (x := 1) and puts x towards the remote location z on node 2 ( $z^2 := x$ ).

Intuitively, when a thread t on n issues remote operations towards node  $\overline{n}$ , one can view these remote operations as if being executed by a thread running in parallel to t. As such, when a remote operation follows a CPU one, the order of the two operations is preserved since the parallel thread is spawned only after the CPU operation is executed. This is illustrated in Fig. 1a. By contrast, when a remote operation precedes a CPU one, the remote operation is performed by a 'separate thread' run in parallel to the later CPU operation in the main thread, and thus may execute before or after the CPU operation, meaning that in the latter case the execution order is not preserved. This is illustrated in Fig. 1b.

Therefore, before using the result of a get or reusing the memory location of a put, it is desirable to avoid such reorderings and to wait for the remote operation to complete. This can be done through a CPU poll operation, poll(n), that blocks until the earliest (in program order) remote operation towards node n has completed. This is shown in Fig. 1c, obtained from Fig. 1b by inserting a poll after the remote operation: poll(2) waits for  $z^2 := x$  to complete before proceeding with x := 1, and thus  $z^2 := x$  can no longer be reordered after x := 1.

Note that each poll(n) waits for *only one* (the earliest) and *not all* pending remote operations towards n to complete. For instance, in Fig. 1d, poll(2) only blocks until the *first*  $z^2 := x$  is complete, and thus z = 1 is once again possible.

| y=0                                                | x=0                                                            | x=0                                              | y=0                                              | x=0        | y=0          | y=0          | x=0          | y=w=0                          | x=z=0        |

|----------------------------------------------------|----------------------------------------------------------------|--------------------------------------------------|--------------------------------------------------|------------|--------------|--------------|--------------|--------------------------------|--------------|

|                                                    |                                                                |                                                  |                                                  |            |              |              |              | $x^2 := 1$                     | $ y^1 := 1 $ |

| $ _{x^2} \cdot = 1$                                | $u^1 \cdot = 1$                                                | $a := u^2$                                       | $b = r^1$                                        | $a := y^2$ | $ b := x^1 $ | $ x^2 := 1 $ | $y^1 := 1$   | $c := z^2$                     | $d := w^1$   |

| $\begin{vmatrix} x^2 := 1 \\ a := y \end{vmatrix}$ | $\begin{vmatrix} y & \cdot - 1 \\ h & \cdot - r \end{vmatrix}$ | $\begin{vmatrix} a & -y \\ x & -1 \end{vmatrix}$ | $\begin{vmatrix} o & -x \\ y & -1 \end{vmatrix}$ | poll(2)    | poll(1)      | pol1(2)      | poll(1)      | $c := z^2$ $poll(2)$ $poll(2)$ | poll(1)      |

| a = g                                              | $0 \cdot - x$                                                  | x .— 1                                           | $ g  \cdot - 1$                                  | x := 1     | y := 1       | a := y       | b := x       | pol1(2)                        | poll(1)      |

|                                                    |                                                                |                                                  |                                                  |            |              |              |              | a := y                         |              |

| (a) $a = b$                                        | b=0 <b>✓</b>                                                   | (b) $a = a$                                      | b=1                                              | (c) a =    | b=1 X        | (d) a =      | b=0 <b>✓</b> | (e) $a =$                      | b=0 X        |

Fig. 2: Concurrent RDMA\* litmus tests.

Two remote operations towards different nodes are independent and can execute in either order, as illustrated in Fig. 1e. The only way to prevent this reordering is to poll the first operation before running the second.

The ordering guarantees on remote operations towards the *same* node are stronger and only certain reorderings are allowed. Recall that a put operation  $x^n := y$  comprises two steps: a local read (on y) and a remote write (on  $x^n$ ). Similarly, a get operation  $x := y^n$  comprises two steps: a remote read (on  $y^n$ ) and a local write (on x). Intuitively, NIC operations follow the *precedence* order: i) local read; ii) remote write; iii) remote read; iv) local write.

If a step with a higher precedence (e.g. a local read) is in program order before one with a lower precedence (e.g. a local write), then their order is preserved and they cannot be reordered. This is illustrated in Fig. 1g. Otherwise the order is not necessarily preserved and these steps can be reordered, as shown in Fig. 1h where an earlier local write on x can occur after the later local read.

As before, the reordering of the two remote operations in Fig. 1h can be prevented by polling the first operation before the second. However, polling is costly as it blocks the current thread, including the submission of remote operations towards any node. Alternatively, we can use a  $remote\ fence$ , rfence(n), that blocks only the NIC and only towards node n. This in turn ensures that earlier (before the fence) remote operations by the thread towards n are executed before later (after the fence) remote operations towards n. This is illustrated in Fig. 1i, obtained from Fig. 1h by inserting rfence(2) stopping the reordering.

Concurrent (Multi-Threaded) RDMA\* Behaviours. The real power of RDMA comes from programs running on different nodes, introducing a wide range of weak behaviours. A network can comprise several nodes, each running several concurrent threads. We limit the examples of Fig. 2 to two nodes, each having a single thread.

As shown in Figs. 2a and 2b, well-known weak behaviours such as store buffering (Fig. 2a) and load buffering (Fig. 2b) are possible. This is because earlier RDMA operations can be delayed after later CPU operations.

As one could expect, most weak behaviours can be prevented by polling the remote operations as needed, as shown for load buffering in Fig. 2c. However, this strategy is not enough to prevent the store buffering weak behaviour, as show in Fig. 2d. This is because the specification of polling offers different guarantees for get and put operations. Polling a get operation  $a := x^n$  offers the strong intuitive guarantee that the operation completed, i.e. the value of  $x^n$  is fetched

from node n and written to a. By contrast, polling a put operation  $x^n := a$  does not guarantee the write on  $x^n$  has completed. When sending the value of a towards node n to be put in  $x^n$ , the remote NIC merely acknowledges having received the data, but this data may still reside in a buffer (i.e. the PCIe fabric) of the remote node, pending to be written  $x^n$ . Polling a put operation only awaits the acknowledgement of the data receipt. As such, it is possible to poll a put operation successfully before the associated remote write has fully completed. In the case of store buffering in Fig. 2d, it is possible for both poll operations to complete before the values of x and y are updated (to 1) in memory.

We also assume NICs are connected to memory though the *Peripheral Component Interconnect Express* (PCIe) fabric, the *de facto* standard for this category of hardware [10]. This ensures that (PCIe) reads cannot overtake (PCIe) writes. As such, a remote read *flushes* (commits) all pending remote writes to memory, and similarly on local memory. This can be used to prevent weak behaviours such as store buffering, as shown in Fig. 2e, obtained from Fig. 2d by adding additional gets and subsequently polling them. Polling a (seemingly unrelated) later get (e.g.  $c := z^2$ ) ensures previous remote writes (e.g.  $x^2 := 1$ ) have been committed to the remote memory.

# 2.2 Robustness: Taming Weak RDMA\* Behaviours

Given the permissive nature of the RDMA\* semantics and the numerous weak behaviours it exhibits (even in the case of single-threaded programs), the task of writing *correct* RDMA programs is laborious. Reasoning about concurrent programs is already challenging even in the absence of weak behaviours. Accounting for potential instruction reorderings (which requires experience with RDMA\* semantics) introduces yet another layer of complexity for developers.

As such, we should ideally enable reasoning about RDMA programs under a simpler, more intuitive model such as SC (sequential consistency [42]). Specifically, to simplify program reasoning, a common approach is to ensure robustness. A program P is robust under a consistency model CM, if its set of possible behaviours under CM coincide with those of its behaviours under SC; i.e. P is robust if it exhibits no weak behaviours. If a program is robust, then we can reason about it  $as\ if$  it were executed under SC, without considering the complexities of RDMA\*.

To ensure robustness, we must prevent *observable* reorderings, i.e. those leading to weak behaviours. We can achieve this through *syntactic* requirements (e.g. by inserting sufficient remote fences and poll operations). A naive solution is to wait for each remote operation to fully complete before proceeding further, thereby preventing all reorderings. Unfortunately, this *serialises* these operations, and thus defeats the benefits of RDMA, which is designed to parallelise CPU instructions and data transfers by offloading them to the NIC. Instead, we should account for the RDMA\* semantics and only add restrictions when necessary, while allowing non-observable reorderings.

Certain reorderings are observable even when considering a single thread in isolation, as in the examples of Figs. 1b, 1e, 1f, and 1h. Specifically, these exam-

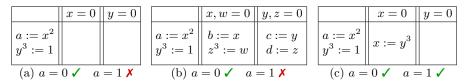

Fig. 3: Examples showing that necessary restrictions depend on other threads.

ples contain data races within a single thread. Beyond robustness, these patterns should be avoided in any sensible program. However, most weak behaviours arise from the interaction of several threads. For instance, in the single-threaded example of Fig. 3a, although the two remote operations  $a:=y^2$  and  $z^3:=1$  on node 1 may be reordered, this reordering is not observable: it does not lead to additional weak behaviours, and thus no additional constraints are necessary for robustness. By contrast, in the multi-threaded variant of Fig. 3b (with a thread on node 2), nodes 2 and 3 can exchange data and thus we can observe the weak behaviour a=1 due to this reordering. As such, to prohibit this, we must prevent the two operations on node 1 from being reordered, e.g. by polling the first operation, as shown in Fig. 3c.

As seen before, preventing reorderings can be done in different ways. In cases like Fig. 1i, a remote fence is enough. In cases like Fig. 2e, we need dummy get operations. Determining when and how to prevent reorderings is not straightforward. As illustrated in the examples of Fig. 3, it cannot be done *thread-locally*: one must account for the communication between other nodes and thus must take the whole program into account. This raises two questions:

- How do we prevent weak behaviours through simple purely syntactic restrictions? Specifically, how can we ensure that a program has enough constraints (e.g. polls) to prevent weak behaviours, and how do we make sure that waiting for a specific remote operation (as in Fig. 3a) is unnecessary?

- How do we structure RDMA programs to minimise the amount of necessary restrictions in order to maintain efficient implementations?

We set out to answer these questions in the remainder of this paper. Specifically, after defining several formal preliminaries in §3, we present a theorem in §4 stating sufficient syntactic conditions guaranteeing robustness (i.e. the absence of weak behaviours). In §5 we then build on this theorem and present a useful RDMA network topology where fewer limitations are necessary to prevent weak behaviours. Notably, following our prescribed network topology ensures that it is never necessary to poll a remote operation to prevent multi-threaded weak behaviours.

# 3 RDMA<sup>SC</sup>: A Declarative Semantics for RDMA Programs

We present the syntax of RDMA programs (taken from [10]) in §3.1. In §3.2 we then present a formal declarative semantics for our RDMA<sup>sc</sup> model. As we

describe in the appendix (§B), we obtain RDMA<sup>SC</sup> by *strengthening* the RDMA<sup>TSO</sup> model of Ambal et al. [10] whereby we make a few simple adjustments to ensure that local (CPU) concurrency follows the SC rather than TSO model.

# 3.1 RDMA<sup>SC</sup>: Programming Language

**Nodes and Threads.** We consider a system with N nodes and M threads in total across all nodes. Let  $\mathsf{Node} = \{1, \dots, N\}$  and  $\mathsf{Tid} = \{1, \dots, M\}$  denote the sets of *node* and *thread identifiers*, respectively. We use n and t to range over  $\mathsf{Node}$  and  $\mathsf{Tid}$ , respectively. Given a node n, we write  $\overline{n}$  to range over  $\mathsf{Node} \setminus \{n\}$ . Each thread  $t \in \mathsf{Tid}$  is associated with a node, written n(t).

**Memory Locations.** Each node n has a set of locations,  $\mathsf{Loc}_n$ , accessible by all nodes. We define  $\mathsf{Loc} \triangleq \biguplus_n \mathsf{Loc}_n$  and  $\mathsf{Loc}_{\overline{n}} \triangleq \mathsf{Loc} \setminus \mathsf{Loc}_n$ . We use  $x^n, y^n, z^n, w^n$  and  $x^{\overline{n}}, y^{\overline{n}}, z^{\overline{n}}, w^{\overline{n}}$  to range over  $\mathsf{Loc}_n$  and  $\mathsf{Loc}_{\overline{n}}$ , respectively. When the choice of n is clear, we write x for  $x^n$  and  $\overline{x}$  for  $x^{\overline{n}}$ . For clarity, we use distinct location names across nodes and write n(x) for the unique  $n \in \mathsf{Node}$  where  $x \in \mathsf{Loc}_n$ . We assume all locations can be accessed by all threads on all nodes. However, for readability, we use a, b, c, and d for (private) locations that are only accessed by a single thread (on a single node).

Values and Expressions. We assume a set of values, Val, with  $\mathbb{N} \subseteq \text{Val}$ , and use v to range over Val. We assume a language of expressions over Val and Loc, and elide its exact syntax and semantics. We use e to range over expressions, and  $e^n$  to range over expressions whose locations are all included in  $\mathsf{Loc}_n$ .

**Sequential Commands and Programs.** Sequential programs on node n are described by the  $C^n$  grammar below and include primitive commands  $(c^n)$ , sequential composition  $(C_1^n; C_2^n)$ , non-deterministic choice  $(C_1^n + C_2^n)$ , executing either  $C_1^n$  or  $C_2^n$ , and non-deterministic loops  $(C^{n*}, C_2^n)$ , executing  $C^n$  any number of times). A (concurrent) program, P, is a map from thread identifiers to commands, associating each thread  $t \in Tid$  with a command on node n(t).

```

\begin{split} \operatorname{\mathsf{Comm}} \ni \mathsf{C}^n &::= \operatorname{\mathsf{skip}} \mid \mathsf{c}^n \mid \mathsf{C}^n_1; \mathsf{C}^n_2 \mid \mathsf{C}^n + \mathsf{C}^n_2 \mid \mathsf{C}^{n*} \quad \operatorname{\mathsf{PComm}} \ni \mathsf{c}^n ::= \mathsf{cc}^n \mid \mathsf{rc}^n \\ \operatorname{\mathsf{CComm}} \ni \mathsf{cc}^n &::= x := e^n \mid \operatorname{\mathsf{assume}}(x = v) \mid \operatorname{\mathsf{assume}}(x \neq v) \\ & \mid x := \operatorname{\mathsf{CAS}}(y, e_1, e_2) \mid \operatorname{\mathsf{poll}}(\overline{n}) \\ \operatorname{\mathsf{RComm}} \ni \mathsf{rc}^n ::= x := \overline{y} \mid \overline{y} := x \mid \operatorname{\mathsf{rfence}}(\overline{n}) \end{split}

```

Primitive commands include CPU ( $\mathsf{cc}^n$ ) and RDMA ( $\mathsf{rc}^n$ ) operations. A CPU operation on n may be a no-op ( $\mathsf{skip}$ ), an assignment to a local location (x := e), an assumption on the value of a local location ( $\mathsf{assume}(x = v)$  and  $\mathsf{assume}(x \neq v)$ ), an atomic CAS ('compare-and-set') operation ( $x := \mathsf{CAS}(y, e_1, e_2)$ ), or a 'poll',  $\mathsf{poll}(\overline{n})$ , that awaits the completion notification of the earliest  $\mathsf{put/get}$  that is pending (not yet acknowledged). An RDMA operation may be (i) a 'get',  $x := \overline{y}$ , reading from remote location  $\overline{y}$  and writing the result to local location x; (ii) a 'put',  $\overline{y} := x$ , reading from local location x and writing the result to remote location  $\overline{y}$ ; or (iii) a 'remote fence',  $\mathsf{rfence}(\overline{n})$ , which ensures that all

later (in program order) RDMA operations towards  $\overline{n}$  will await the completion of all earlier RDMA operations towards  $\overline{n}$ . poll( $\overline{n}$ ) is executed by the CPU and blocks its thread (and prevents the requests of later remote operations), while rfence( $\overline{n}$ ) blocks the NIC for the execution of remote operations towards  $\overline{n}$ .

### 3.2 RDMA<sup>SC</sup>: Declarative Semantics

**Events and Executions.** In the literature of declarative models, the traces of a program are commonly represented as a set of *executions*, where an execution is a graph comprising: i) a set of *events* (graph nodes); and ii) a number of relations on events (graph edges). Each event is associated with the execution of a primitive command (in PComm) and is a tuple  $(\iota, t, l)$ , where  $\iota$  is the (unique) *event identifier*,  $t \in \mathsf{Tid}$  identifies the executing thread, and  $l \in \mathsf{ELab}$  is the *event label*, defined below.

**Definition 1 (Labels and events).** An event,  $e \in \text{Event}$ , is a triple  $(\iota, t, l)$ , where  $\iota \in \mathbb{N}$ ,  $t \in \text{Tid}$  and  $l \in \text{ELab}_{n(t)}$ . The set of event labels is  $\text{ELab} \triangleq \bigcup_n \text{ELab}_n$  for all nodes n. An event label of n,  $l \in \text{ELab}_n$ , is a tuple of one of the following forms:

```

\begin{array}{lll} - & NIC \; local \; read: \; l = \mathtt{nlR}(x^n, v_r, \overline{n}) & - \; (CPU) \; local \; read: \; l = \mathtt{lR}(x^n, v_r) \\ - & NIC \; remote \; write: \; l = \mathtt{nrR}(y^{\overline{n}}, v_w) & - \; (CPU) \; local \; write: \; l = \mathtt{lW}(x^n, v_w) \\ - & NIC \; local \; write: \; l = \mathtt{nlW}(x^n, v_w, \overline{n}) & - \; (CPU) \; CAS: \; l = \mathtt{CAS}(x^n, v_r, v_w) \\ - & NIC \; fence: \; l = \mathtt{nF}(\overline{n}) & - \; (CPU) \; poll: \; l = \mathtt{P}(\overline{n}) \end{array}

```

Each event label denotes whether the associated primitive command is handled by the NIC (left column, prefixed with n), or the CPU (right column). A poll instruction is handled by the CPU. A put operation  $x^{\overline{n}} := y^n$  by node n towards node  $\overline{n}$  comprises a NIC local read from  $y^n$  and a NIC remote write on  $x^{\overline{n}}$  and is thus modelled as two events with labels  $\mathtt{nlR}(y^n,v,\overline{n})$  and  $\mathtt{nrW}(x^{\overline{n}},v)$ , where v denotes the value read from  $y^n$  and written to  $x^{\overline{n}}$ . Similarly, a get  $x^n := y^{\overline{n}}$  is modelled as two events with labels of the form  $\mathtt{nrR}(y^{\overline{n}},v)$  and  $\mathtt{nlW}(x^n,v,\overline{n})$ .

CPU operations are modelled by events as expected. A successful operation  $x := \mathtt{CAS}(y, v_1, v_2)$  is modelled by two events with labels  $\mathtt{CAS}(y, v_1, v_2)$  and  $\mathtt{lW}(x, v_1)$ . An unsuccessful  $x := \mathtt{CAS}(y, v_1, v_2)$  operation is modelled by a CPU read instead:  $\mathtt{lR}(y, v)$  and  $\mathtt{lW}(x, v)$ , with  $v \neq v_1$ .

We write  $\mathsf{type}(l)$ ,  $\mathsf{loc}(l)$ ,  $v_{\mathsf{r}}(l)$ ,  $v_{\mathsf{w}}(l)$ , and  $\overline{n}(l)$  for the type (e.g. 1R), location, read value, write value, and remote node of l, where applicable; e.g.  $\mathsf{loc}(\mathsf{nlR}(x^n,v_{\mathsf{r}},\overline{n})) = x^n$  and  $\overline{n}(\mathsf{nlR}(x^n,v_{\mathsf{r}},\overline{n})) = \overline{n}$ . We lift these functions to events as expected. We write  $\iota(\mathsf{e})$ ,  $\iota(\mathsf{e})$ ,  $\iota(\mathsf{e})$  to project the corresponding components of an event  $\mathsf{e} = (\iota,t,l)$ , and write  $\iota(\mathsf{e})$  for the node  $\iota(\mathsf{e})$  of an event.

Queue Pairs. As mentioned in §2 (see Fig. 1e), two remote operations by the same thread towards different remote nodes can be reordered. When using RDMA, each thread establishes a communication channel, called a *queue pair*, towards each remote node. The intuition is that operations on different queue pairs are independent and can always be reordered. Different threads, even on the same node, create different queue pairs to connect to the same remote node.

**Notation.** Given a relation r and a set A, we write  $r^+$  for the transitive closure of r;  $r^{-1}$  for the inverse of r;  $r|_A$  for  $r \cap (A \times A)$ ; and [A] for the identity relation on A, i.e.  $\{(a,a) \mid a \in A\}$ . We write  $r_1; r_2$  for their relational composition:  $\{(a,b) \mid \exists c. (a,c) \in r_1 \land (c,b) \in r_2\}$ . When r is a strict partial order, we write  $r|_{\text{imm}}$  for the *immediate* edges in r, i.e.  $r \setminus (r;r)$ . Given a set of events E and a location x, we write  $E_x$  for  $\{e \in E \mid loc(e) = x\}$ . Given a set of events E and a label type X, we write E.X for  $\{e \in E \mid type(e) = X\}$ , and define its sets of reads as  $E.\mathcal{R} \triangleq E.\mathtt{lR} \cup E.\mathtt{CAS} \cup E.\mathtt{nlR} \cup E.\mathtt{nrR}$ , writes as  $E.\mathcal{W} \triangleq$  $E.1W \cup E.CAS \cup E.n1W \cup E.nrW$ , CPU events as  $E^{cpu} \triangleq E.1W \cup E.1R \cup E.CAS \cup E.P$ , and NIC writes as  $E.nW \triangleq E.nlW \cup E.nrW$ . We define the 'same-location' relation as  $sloc \triangleq \{(e, e') \in Event^2 | loc(e) = loc(e')\};$  the 'same-thread' relation as sthd  $\triangleq \{(e, e') \in \text{Event}^2 \mid t(e) = t(e')\};$  and the 'same-queue-pair' relation as  $\operatorname{sqp} \triangleq \{(e, e') \in \operatorname{Event}^2 \mid t(e) = t(e') \land \overline{n}(e) = \overline{n}(e')\}.$  We use  $\operatorname{sqp}$  for events on the same queue pair, i.e. by the same thread and towards the same remote node. Note that  $sqp \subseteq sthd$  and that sloc, sthd, and sqp are all symmetric. For a set of events E, we write E.sloc for  $\operatorname{sloc}_{|E|}$ ; similarly for E.sthd and E.sqp.

**Definition 2 (Pre-executions).** A tuple  $\mathcal{G} = \langle E, po, pf \rangle$  is a pre-execution of a program if:

- $-E \subseteq \mathsf{Event}$  is the set of events and includes a set of initialisation events,  $E^0 \subseteq E$ , comprising a single write with label  $\mathtt{lW}(x,0)$  for each  $x \in \mathsf{Loc}$ .

- po  $\subseteq E \times E$  is the 'program order' relation defined as a disjoint union of strict total orders, each ordering the events of one thread, with  $E^0 \times (E \setminus E^0) \subseteq$  po, and such that:

- Each put (resp. get) operation corresponds to two events: a read and a write with the read immediately preceding the write in po: 1. if  $r \in G.nlR$  (resp.  $r \in G.nrR$ ), then  $(r, w) \in po|_{imm}$  for some  $w \in G.nrW$  ( $w \in G.nlW$ ); and 2. if  $w \in G.nrW$  (resp.  $w \in G.nlW$ ), then  $(r, w) \in po|_{imm}$  for some  $r \in G.nlR$  ( $r \in G.nrR$ ).

- Read and write events of a put (resp. get) have matching values: if  $(r,w) \in G.\mathsf{po}|_{imm}$ ,  $\mathsf{type}(r) \in \{\mathsf{nlR},\mathsf{nrR}\}$ , and  $\mathsf{type}(w) \in \{\mathsf{nlW},\mathsf{nrW}\}$ , then  $v_r(r) = v_w(w)$ .

- pf ⊆ E.nW × E.P is the 'polls-from' relation, relating earlier (in programorder) NIC writes to later poll operations on the same queue pair; i.e. pf ⊆ po ∩ sqp. Moreover, pf is functional on its domain (every NIC write can be be polled at most once), and pf is total and functional on its range (every poll in E.P polls from exactly one NIC write). Also, Poll events poll-from the oldest non-polled remote operation on the same queue pair:

- if  $w_1 \in G.nW$  and  $w_1 \xrightarrow{po \cap sqp} w_2 \xrightarrow{pf} p_2$ , then there exists  $p_1$  such that  $w_1 \xrightarrow{pf} p_2$ .

Pre-executions are constructed syntactically by induction on the structure of the corresponding program. This definition is standard and omitted.

Intuitively, a pre-execution can also be seen as a trace of the execution: for each thread t, po restricted to t is a total order, and so  $\langle E, po \rangle$  is fundamentally

a sequence of events for each thread. In this view, pf should be considered a well-formedness condition: each prefix of the trace needs to have at least as many remote operations as poll operations. So  $\langle E, po, pf \rangle$  can be seen as providing a well-formed trace for each thread. We later define robustness conditions on pre-executions, and as such they can also be considered conditions on traces.

We next extend the notion of a pre-execution to an *execution* by choosing explicitly how the different events interact.

**Definition 3 (Executions).**  $G = \langle E, po, pf, rf, mo, nfo \rangle$  is an execution if:

- $-\langle E, po, pf \rangle$  is a pre-execution.

- rf  $\subseteq E.W \times E.R$  is the 'reads-from' relation on events of the same location with matching values; i.e.  $(a,b) \in \mathsf{rf} \Rightarrow (a,b) \in \mathsf{sloc} \land v_w(a) = v_r(b)$ . Moreover, rf is total and functional on its range: every read in E.R is related to exactly one write in E.W.

- $\text{ mo} \triangleq \bigcup_{x \in \mathsf{Loc}} \mathsf{mo}_x$  is the 'modification-order', where each  $\mathsf{mo}_x$  is a strict total order on  $E.\mathcal{W}_x$  with  $E_x^0 \times (E.\mathcal{W}_x \setminus E_x^0) \subseteq \mathsf{mo}_x$  describing the order in which writes on x reach the memory.

- nfo  $\subseteq E.$ sqp is the 'NIC flush order', such that for all  $(a,b) \in E.$ sqp, if  $a \in E.$ nlR,  $b \in E.$ nlW, then  $(a,b) \in$  nfo  $\cup$  nfo<sup>-1</sup>, and if  $a \in E.$ nrR,  $b \in E.$ nrW, then  $(a,b) \in$  nfo  $\cup$  nfo<sup>-1</sup>.

We define the *reads-before* relation as  $\mathsf{rb} \triangleq (\mathsf{rf}^{-1}; \mathsf{mo}) \setminus [E]$ , relating each read r to writes that are  $\mathsf{mo}$ -after the write r reads from. Given a (pre-)execution G (resp.  $\mathcal{G}$ ), we use the 'G.' prefix to project its various components (e.g. G. $\mathsf{rf}$ ) and derived relations (e.g. G. $\mathsf{rb}$ ). When the context is clear, we drop the prefix.

PCIe guarantees that a NIC local read (nlR) propagates all pending NIC local writes (nlW) (processed by the same queue pair) to memory, while a NIC remote read (nrR) propagates all pending NIC remote writes (nrW) (processed by the same queue pair) to memory. We model this total order through the nfo relation, stipulating that all NIC local reads and writes (resp. all NIC remote reads and writes) on the same queue pair be totally ordered.

Issue and Observation Points. In what follows we distinguish between when an instruction is issued and when it is observed. Intuitively, an instruction is issued when it is processed by the CPU or the NIC, and it is observed when its effect is propagated to memory. As such, since NIC writes can be delayed and have an observable effect on memory, the time points at which they are issued and observed may differ. Since we assume CPUs follow the strong SC memory model, CPU writes are issued and observed at the same time. However, the local (resp. remote) write of a get (resp. put) is issued when it is processed by the NIC and sent to the PCIe fabric, and observed when it is propagated to memory. All other events are instantaneous in that either they do not have an observable effect on memory (e.g. reads), or their effect is written to memory immediately (e.g. CAS operations and CPU writes). Given a set of events E, we thus define the set of instantaneous events in E as E.Inst  $\triangleq E \setminus (E.nlW \cup E.nrW)$ . Intuitively, the effects of NIC local writes and NIC remote writes (labelled nlW and nrW) can be delayed in the PCIe fabric and are thus excluded from the set

|         | Later in Program Order |                  |                  |                      |                |                      |     |                      |  |  |

|---------|------------------------|------------------|------------------|----------------------|----------------|----------------------|-----|----------------------|--|--|

|         | ippo                   |                  | 1                | 2                    | 3              | 4                    | 5   | 6                    |  |  |

|         |                        |                  | $E^{\text{cpu}}$ | nlR                  | $\mathtt{nrW}$ | nrR                  | nlW | nF                   |  |  |

| 0       | $ \mathbf{A} $         | $E^{\text{cpu}}$ | <b>√</b>         | >                    | <b>√</b>       | >                    | 1   | <b>✓</b>             |  |  |

| Ъ       | В                      | nlR              | X                | $\operatorname{sqp}$ | sqp            | $\operatorname{sqp}$ | sqp | $\operatorname{sqp}$ |  |  |

| in      | $ \mathbf{C} $         | nrW              | X                | X                    | sqp            | $\operatorname{sqp}$ | sqp | $\operatorname{sqp}$ |  |  |

| lieı    | $\mathbf{D}$           | nrR              | X                | X                    | X              | X                    | sqp | $\operatorname{sqp}$ |  |  |

| Earlier | $\mathbf{E}$           | nlW              | X                | X                    | X              | X                    | sqp | $\operatorname{sqp}$ |  |  |

| щ       | $\mathbf{F}$           | nF               | X                | $\operatorname{sqp}$ | sqp            | $\operatorname{sqp}$ | sqp | sqp                  |  |  |

| Later in Program Order |              |                    |                  |                      |                      |                      |                      |                      |  |

|------------------------|--------------|--------------------|------------------|----------------------|----------------------|----------------------|----------------------|----------------------|--|

| onno                   |              |                    | 1                | 2                    | 3                    | 4                    | 5                    | 6                    |  |

|                        | oppo         |                    | $E^{\text{cpu}}$ | nlR                  | nrW                  | nrR                  | nlW                  | nF                   |  |

| 0                      | A            | $E^{\mathrm{cpu}}$ | <b>✓</b>         | <b>\</b>             | <b>√</b>             | >                    | <b>√</b>             | <b>√</b>             |  |

| 1 P                    | В            | nlR                | X                | $\operatorname{sqp}$ | sqp                  | $\operatorname{sqp}$ | sqp                  | $\operatorname{sqp}$ |  |

| i.                     | $\mathbf{C}$ | nrW                |                  | X                    | $\operatorname{sqp}$ | $\operatorname{sqp}$ | $\operatorname{sqp}$ | X                    |  |

| lier                   | $\mathbf{D}$ | nrR                | X                | Х                    | Х                    | X                    | $\operatorname{sqp}$ | $\operatorname{sqp}$ |  |

| Earlier                | $\mathbf{E}$ | nlW                | X                | Х                    | Х                    | X                    | $\operatorname{sqp}$ | X                    |  |

| щ                      | F            | nF                 | X                | $\operatorname{sqp}$ | $\operatorname{sqp}$ | $\operatorname{sqp}$ | $\operatorname{sqp}$ | $\operatorname{sqp}$ |  |

Fig. 4: The RDMA<sup>SC</sup> ordering constraints on ippo (left) and oppo (right), where  $\checkmark$  denotes that instructions are ordered (and cannot be reordered),  $\checkmark$  denotes they are not ordered (and may be reordered), and sqp denotes they are ordered iff they are on the same queue pair.

of instantaneous events. Note that the observation point either follows the issue point (for NIC writes), or coincides (for instantaneous events).

We next define the 'issue-preserved program order', ippo, as the subset of po edges (ippo  $\subseteq$  po) that must be preserved when issuing instructions. That is, if two events are ippo-related, then they must be issued in program order; otherwise they may be processed in either order. The left table of Fig. 4 describes which po edges are included in ippo, where  $\checkmark$  denotes that the two instructions are ippo-related (i.e. they must be issued in program order),  $\checkmark$  denotes that they are not ippo-related (i.e. they may be issued out of order) and sqp denotes that they are ippo-related iff they are on the same queue pair. For instance, when a CPU instruction is followed by anything, they are issued in order (line A); but when a NIC instruction is followed by a CPU one, they may be reordered (cells B1-F1).

Analogously, we define the 'observation-preserved program order', oppo, as the subset of po edges (oppo  $\subseteq$  po) that must be preserved when observing the effects of instructions. I.e., if two events are oppo-related, then they become observable in program order in RDMA<sup>SC</sup>; otherwise they may become observable in either order. The right table of Fig. 4 describes which po edges are included in oppo. The two tables differ in cells C6 and E6. This is because NIC writes can be delayed, and remote fences do not guarantee propagation to memory.

RDMA<sup>SC</sup> Consistency. The notion of executions (Def. 3) imposes very few constraints on the po, pf, rf, mo, and nfo relations. Such restrictions and thus the permitted behaviours of a program are determined by defining the set of *consistent* executions, defined below.

**Definition 4 (RDMA**<sup>SC</sup>-consistency). An execution  $\langle E, po, pf, rf, mo, nfo \rangle$  is RDMA<sup>SC</sup>-consistent iff ib and ob are irreflexive, where:

The ib (resp. ob) relation is an extension of ippo (resp. oppo), describing the issue (resp. observation) order across the instructions of different threads and nodes. RDMA<sup>SC</sup>-consistency requires that ib and ob be irreflexive (i.e. yield strict partial orders as they are defined transitively).

The rf (resp. pf) component in ib states that if e reads from (resp. polls from) w, then w must have been issued before e. Recall that nfo totally orders the nlR/nlW and nrR/nrW operations on the same queue pair and is thus in ib. The rf component in ob states that if a read r reads from a write w, then the write has reached memory. This is because reads can only read the main memory and not auxiliary buffers. The [nlW]; pf component states that if p polls from a NIC local write w, then w must have left the PCIe fabric and reached the memory. Note that this is not the case for nrW events: polling an nrW event w might succeeds when w is still in the remote PCIe fabric before reaching the remote memory. The nfo in ob can be justified as in the case of ib. The rb component in ob ensures that a read r on x observes the latest write on x that has reached the memory. As mo describes the order in which the writes on each location reach the memory, it is included in ob. Let  $(\tau_i, \tau_o)$  be the issue and observation points of e and  $(\tau_i', \tau_o')$  be those of e'. The [Inst]; ib in ob ensures that if  $e \stackrel{\text{ib}}{\rightarrow} e'$  (i.e.  $\tau_i' < \tau_i'$ ) and e is instantaneous  $(\tau_i = \tau_o)$ , then  $\tau_o = \tau_i < \tau_i' \le \tau_o'$ , i.e.  $e \stackrel{\text{ob}}{\rightarrow} e'$ .

# 4 Robustness of RDMA<sup>SC</sup> Programs

In the traditional setting of CPU concurrency (where all threads execute CPU instructions), the most intuitive consistency model is *sequential consistency* (SC) [42] While SC is too strong—in that disallowing *all* reorderings does not enable efficient implementations—it provides an intuitive and commonly understood model, making it easier for developers to reason about their programs.

Although none of the existing well-known consistency models follow SC by default, programmers typically address this difficulty by focusing on *robust* implementations of algorithms. Specifically, a program is robust under a weak consistency model CM if every possible behaviour of the program under CM is also an allowed behaviour under SC. In our model, this is defined as follows.

**Definition 5 (SC-consistency and RDMA**<sup>SC</sup>-robustness). Given an execution  $\langle E, po, pf, rf, mo, nfo \rangle$ , its associated sequential-consistency relation is defined as  $sc \triangleq (po \cup rf \cup rb \cup mo)$ . An execution G is SC-consistent iff G.sc is acyclic. A pre-execution is robust under RDMA<sup>SC</sup> iff all of its RDMA<sup>SC</sup>-consistent executions (Def. 4) are also SC-consistent.

Our aim here is to provide guidelines to ensure the robustness of RDMA<sup>SC</sup> programs. That is, we identify a number of *syntactic* requirements such that if a program fulfils them, then the behaviours of the program under RDMA<sup>SC</sup> coincide with its behaviours under SC; i.e. the program does not exhibit any weak behaviours brought about by observable reorderings.

There are two complementary approaches to achieve robustness. The first is to structure the program in a way that limits the very existence of problematic

|         |                         |     |                      |     | Late: | r in | ро       |          |                 |          |     |  |

|---------|-------------------------|-----|----------------------|-----|-------|------|----------|----------|-----------------|----------|-----|--|

|         |                         |     | different queue pair |     |       |      |          |          | same queue pair |          |     |  |

|         | gb                      |     | 1                    | 2   | 3     | 4    | 5        | 6        | 7               | 8        | 9   |  |

|         |                         |     | CPU                  | nlR | nrW   | nrR  | nlW      | nlR      | nrW             | nrR      | nlW |  |

| bo      | A                       | CPU | <b>✓</b>             | 1   | 1     | 1    | <b>/</b> |          | $N_{i}$         | /A       |     |  |

| Щ.      | В                       | nlR | Р                    | Р   | Р     | Р    | Р        | <b>\</b> | <b>\</b>        | <b>✓</b> | 1   |  |

| er      | $\mathbf{C}$            | nrW | GP                   | GP  | GP    | GP   | GP       | GP       | <b>✓</b>        | <b>√</b> | 1   |  |

| Earlier | $\overline{\mathbf{D}}$ | nrR | Р                    | Р   | Р     | Р    | Р        | F        | F               | F        | 1   |  |

| 茁       | E                       | nlW | Р                    | Р   | Р     | Р    | Р        | F        | F               | Р        | 1   |  |

Fig. 5: Constraints necessary to guarantee that a pair of po-related events in  $\mathcal{R} \cup \mathcal{W}$  will be ob-related for any consistent execution. CPU denotes local events in  $1 \text{W} \cup 1 \text{R} \cup \text{CAS}$ . The  $\checkmark$  denotes that no additional constraint is needed and that the events are already in ob. P denotes that the earlier operation must be polled before executing the later one. F denotes that either the earlier operation must be polled (similar to P) or that a remote fence must be inserted between the two operations. GP denotes that a get operation and its associated poll on the first queue pair must be inserted between the two operations.

cases. The second is to extend the program with enough restrictions (e.g. polls and remote fences) to prohibit reorderings. In the next section (§5) we focus on the former and provide a set of explicit guidelines to avoid most problematic cases by design. In this section we focus on the latter, and describe how to identify problematic cases and how to block them. In what follows, we present the general syntactic restrictions required to forbid the reordering opportunities for specific operations (§4.1). We then propose sufficient syntactic conditions that block observable reorderings, and we prove that these conditions imply robustness (§4.2). Finally, we discuss the limitations of this approach (§4.3).

#### 4.1 A Syntactic Approach to Enforce the Program Order

One of our key results relies on enforcing the program order (i.e. blocking instruction reordering) in potentially observable cases. Recall that given an execution, the observed-before order (ob) describes when an event takes effect before another. That is, for  $(e_1, e_2) \in po$ , when  $e_1 \xrightarrow{ob} e_2$  in an execution G, then they are not reordered in G. Our first aim here is to identify syntactic constraints that ensure that a specific pair of given instructions (of the same thread) are related by ob. However, in order to define syntactic constraints for robustness, we can only rely on the syntax of the program and not components such as rf or mo. Our syntactic constraints can only rely on the pre-execution components po and pf, and we cannot directly use the ob relation derived from a specific execution.

To this end, we first define the *guaranteed-before* relation,  $\mathsf{gb} \subseteq \mathsf{po}$ , describing when two instructions in the same thread are guaranteed to remain in order (and their reordering is blocked), as shown in Fig. 5. Specifically, if two instructions are related by  $\mathsf{oppo}$ , then they are guaranteed to be observed in that order and

thus there is no need for additional restrictions; this is denoted by  $\checkmark$  in cells A1–A5, B6–B9, C7–C9, D9, and E9 (*cf.* oppo in Fig. 4). For most other cases (noted P or F), polling the earlier instruction enforces the ordering. Recall that polling a NIC remote write does not guarantee its completion, and we need to add a 'dummy' get operation and its corresponding poll to ensure ordering (noted GP).

In most cases, when the two operations are on the *same* queue pair, then a remote fence is sufficient to enforce the ordering (noted F in D6–D8, E6–E7), and is a cheaper alternative to a poll. Perhaps surprisingly, a remote fence is not always sufficient: the two outliers are cells C6 and E8. For C6, consider the program  $z^2 := x$ ; rfence(2);  $w^2 := y$ : the local value of y might be read before the value of z is changed. This is because rfence (2) (as with poll) only awaits the acknowledgement from the remote side which does not necessarily ensure that the first put has completed. For E8, consider  $x := z^2$ ; rfence(2);  $y := w^2$ , where  $w^2$  can be read before x is modified: rfence (2) only waits for the NIC local write  $(x := v_z)$  to be sent to the local PCIe fabric and thus the put operation  $(y := w^2)$  can start earlier than one could expect.

**Definition 6 (guaranteed-before).** Given a pre-execution  $\mathcal{G} = \langle E, \mathsf{po}, \mathsf{pf} \rangle$ , its guaranteed-before order,  $\mathsf{gb} \subseteq \mathsf{po}$ , is defined as  $\mathsf{gb} \triangleq \mathsf{gb}_{\mathsf{base}}^+$ , with:

```

\begin{array}{lll} {\sf gb_{base}} \triangleq & {\sf oppo} & ({\rm A1-A5,B6-B9,C7-C9,D9,E9 \ in \ Fig. \ 5}) \\ & \cup [{\sf n1R}]; {\sf po|}_{imm}; [{\sf nrW}]; {\sf pf} & ({\rm B1-B5 \ in \ Fig. \ 5}) \\ & \cup [{\sf nrW}]; ({\sf po} \cap {\sf sqp}); [{\sf n1W}]; {\sf pf} & ({\rm C1-C6 \ in \ Fig. \ 5}) \\ & \cup [{\sf nrR}]; {\sf po|}_{imm}; [{\sf n1W}]; {\sf pf} & ({\rm D1-D8 \ in \ Fig. \ 5}) \\ & \cup [{\sf n1W}]; ({\sf po} \cap {\sf sqp}); [{\sf nF}]; ({\sf po} \cap {\sf sqp}) & ({\rm D6-D8 \ in \ Fig. \ 5}) \\ & \cup [{\sf n1W}]; {\sf pf} & ({\rm E1-E8 \ in \ Fig. \ 5}) \\ & \cup [{\sf n1W}]; ({\sf po} \cap {\sf sqp}); [{\sf nF}]; ({\sf po} \cap {\sf sqp}); [{\sf n1R} \cup {\sf nrW}] & ({\rm E6-E7 \ in \ Fig. \ 5}) \end{array}

```

Given an execution  $G = \langle E, \mathsf{po}, \mathsf{pf}, \mathsf{rf}, \mathsf{mo}, \mathsf{rb} \rangle$ , we write  $G.\mathsf{gb}$  for  $\langle E, \mathsf{po}, \mathsf{pf} \rangle.\mathsf{gb}$ . Finally, we prove that  $\mathsf{gb}$  implies  $\mathsf{ob}$  for any RDMA<sup>SC</sup>-consistent execution (see Theorem 7 for the proof).

**Theorem 1** (gb implies ob). Given a pre-execution  $\langle E, \mathsf{po}, \mathsf{pf} \rangle$ , for all RDMA<sup>SC</sup>-consistent executions  $G = \langle E, \mathsf{po}, \mathsf{pf}, \mathsf{rf}, \mathsf{mo}, \mathsf{nfo} \rangle$  and all  $\mathsf{e}_1, \mathsf{e}_2 \in E$ , if  $(\mathsf{e}_1, \mathsf{e}_2) \in G.\mathsf{gb}$ , then  $(\mathsf{e}_1, \mathsf{e}_2) \in G.\mathsf{ob}$ .

Given Theorem 1 above, we can use gb as a tool to enforce robustness. Specifically, whenever a program order pair  $(e_1,e_2) \in po$  may be reordered, we can add the prescribed fences to enforce  $(e_1,e_2) \in gb$  and thus block the reordering. The rest of this section describes when we should use this tool.

# 4.2 Conditions for Robustness under RDMA<sup>SC</sup>

As mentioned before, blocking all instruction reorderings, i.e. by requiring po = gb, would enforce sequential consistency and thus robustness. However, this is too strict and highly impractical. Instead, we should ideally enforce gb selectively when needed and only prevent observable reorderings.

Two sources of weak behaviours. As presented in §2, RDMA<sup>SC</sup> programs have two distinct sources of weak behaviours. These come from two different kinds of pairs of events (of the same thread): (1) pairs forming a data race on a certain location, e.g.  $a := y^2; y^2 := 1$ , as presented in Fig. 1f (copied below-left) and Figs. 1b, 1e, and 1h; and (2) pairs whose reordering can be observed by other threads, e.g.  $a := y^2; z^3 := 1$ , as in the examples of Fig. 3b (copied below-right).

|                       | y=0 |

|-----------------------|-----|

| $a := y^2$ $y^2 := 1$ |     |

| a = 1                 | 1   |

|                                                      | y = 0      | z = 0 |  |  |  |  |

|------------------------------------------------------|------------|-------|--|--|--|--|

| $\begin{vmatrix} a := y^2 \\ z^3 := 1 \end{vmatrix}$ | $y := z^3$ |       |  |  |  |  |

| $a=1$ $\checkmark$                                   |            |       |  |  |  |  |

As such, stopping these two sources of weak behaviours would be enough to ensure robustness. Data races within a thread are always problematic, no matter the context, and we always need to block the reordering of such pairs (i.e. enforce gb to ensure the pair is ob-ordered in any execution). Pairs of the second kind cannot create weak behaviours by themselves, but they might allow weak behaviours depending on the rest of the program of other threads. In the next section (§5), we show conditions making sure that such pairs can never create weak behaviours by design. In this section, we focus on deciding whether such a pair might lead to a weak behaviour and, if so, how to block the reordering.

To formulate this intuition, we write public(x) to denote that x is a public location accessed by multiple threads, and given a set of events E, we define the set of public events in E as  $E^{\text{pub}} \triangleq \{e \in E \mid \text{public}(\log(e))\}$ . We further define  $E \setminus t \triangleq \{e \in E \mid t(e) \neq t\}$  for the set of events in E that are not by thread t. We can then formulate the two categories of weak behaviours above as two kinds of sc cycles: sc cycles on a single thread (1) and sc cycles on public events across threads (2), as formulated below (see Theorem 8 for the full proof).

Theorem 2 (sc cycle decomposition). Given a RDMA<sup>SC</sup>-consistent execution  $G = \langle E, po, pf, rf, mo, nfo \rangle$ ,  $if \exists e \in E. e \xrightarrow{G.sc}^+ e$  (i.e. a cycle in G.sc), then:

- $\begin{array}{lll} \ \ either \ there \ is \ a \ G.sc \ \ cycle \ on \ a \ single \ thread, \ i.e. \ \exists e \in E. \ e \xrightarrow{G.sc \cap sthd}^+ e; \\ \ \ or \ there \ \ exists \ e_1, e_2 \in E^{pub} \ \ such \ that \ e_1 \xrightarrow{po \setminus G.ob} e_2 \xrightarrow{(G.sc; [E^{pub} \setminus t(e_1)])^+; G.sc} e_1. \end{array}$ That is, there is an sc cycle on public events, with two po-related events on some thread  $t(e_1)$  not related in ob, and where the rest of the cycle does not go through the events of  $t(e_1)$ .

The two kinds of problematic reorderings are tackled separately below, and Theorem 5 confirms the two resulting conditions are sufficient for robustness.

Preventing sc cycles from data races. As shown above, when an allowed reordering is part of a data race, it becomes observable independently from the context. Thus, we should always preclude this kind of reordering. Specifically, in Def. 7 below we present a local data-race freedom property to block data races within each thread and prevent single-threaded weak behaviours.

**Definition 7 (Local DRF).** Given a pre-execution  $\langle E, \mathsf{po}, \mathsf{pf} \rangle$ , two events  $\mathsf{e}_1, \mathsf{e}_2 \in E$  are locally conflicting iff 1.  $(\mathsf{e}_1, \mathsf{e}_2) \in \mathsf{sthd}$ ; 2.  $\mathsf{loc}(\mathsf{e}_1) = \mathsf{loc}(\mathsf{e}_2)$ ; and 3. at least one of  $\mathsf{e}_1, \mathsf{e}_2$  is a write event. A pre-execution  $\mathcal G$  is locally datarace free (LDRF), iff for all  $\mathsf{e}_1, \mathsf{e}_2 \in \mathcal G.E$ , if  $\mathsf{e}_1, \mathsf{e}_2$  are locally conflicting, then  $(\mathsf{e}_1, \mathsf{e}_2) \in \mathcal G.\mathsf{gb} \cup \mathcal G.\mathsf{gb}^{-1}$ . Put differently, given the definition of  $\mathsf{gb}$  (Fig. 5), a pre-execution  $\langle E, \mathsf{po}, \mathsf{pf} \rangle$  is LDRF iff for all locally conflicting accesses  $\mathsf{e}_1, \mathsf{e}_2 \in E$ , if  $(\mathsf{e}_1, \mathsf{e}_2) \in \mathsf{po}$ , then the following four conditions hold:

- 1. If  $e_1 \in nlW$  and  $(e_1, e_2) \notin sqp$ , then there exists  $e_3 \in P$  such that  $(e_1, e_3) \in pf$  and  $(e_3, e_2) \in po$  (cells E1, E2, and E5 in Fig. 5).

- 2. If  $e_1 \in nlW$ ,  $e_2 \in nlR$ , and  $(e_1, e_2) \in sqp$ , then either there exists  $e_3 \in P$  with  $(e_1, e_3) \in pf$  and  $(e_3, e_2) \in po$ ; or there exists  $e_3 \in nF$  with  $(e_1, e_3) \in po$  and  $(e_3, e_2) \in po$  (E6).

- 3. If  $e_1 \in nlR$ ,  $e_2 \in (nlW \cup lW \cup CAS)$ , and  $(e_1, e_2) \not\in sqp$ , then there exists  $e_1' \in nrW$  and  $e_3 \in P$  such that  $(e_1, e_1') \in po|_{imm}$ ,  $(e_1', e_3) \in pf$ , and  $(e_3, e_2) \in po$  (cells B1 and B5).

- 4. If  $e_1 \in nrR$  and  $e_2 \in nrW$ , then either there exists  $e_3 \in nF$  such that  $e_1 \xrightarrow{po \cap sqp} e_3 \xrightarrow{po \cap sqp} e_2$ ; or there exists  $e_1' \in nlW$  and  $e_3 \in P$  such that  $e_1 \xrightarrow{po|_{imm}} e_1' \xrightarrow{pf} e_3 \xrightarrow{po} e_2$  (cell D7 in Fig. 5).

These cases prohibit all possible races on a location x, i.e. of the form  $x := y^n; x := -(E1,E5), x := y^n; -:= x (E2), x := y^n; z^n := x (E6), y^n := x; x := -(B1,B5), or <math>-:= x^n; x^n := -(D7)$ . Other entries in Fig. 5 cannot create races as either their ordering is already guaranteed (e.g.  $\checkmark$  in E9); or they are on two read events (e.g. B2,D8); or they cannot be on the same location (e.g. D3,E7).

We argue that the constraints in Def. 7 do not restrict RDMA capabilities in that waiting for remote operations to complete before reusing their locations is already considered standard practice when writing RDMA programs.

We next show that LDRF prevents single-threaded weak behaviours (see Theorem 9 for the proof).

**Theorem 3.** Given a RDMA<sup>SC</sup>-consistent execution  $G = \langle E, \mathsf{po}, \mathsf{pf}, \mathsf{rf}, \mathsf{mo}, \mathsf{nfo} \rangle$ , if  $\langle E, \mathsf{po}, \mathsf{pf} \rangle$  is locally data-race free, then there is no sc cycle on a single thread; that is,  $(G.\mathsf{sc} \cap \mathsf{sthd})$  is acyclic and the first case of Theorem 2 does not arise.

Preventing sc cycles across threads. Unlike data races, pairs of the second kind cannot create weak behaviours by themselves, and their reorderings can only be observed in certain contexts.

The general strategy to prevent observable reorderings is straightforward: for every pair  $(e_1, e_2) \in po$  on public locations, either we know for certain that  $e_2 \stackrel{sc}{\longrightarrow}^* e_1$  (using other threads) is impossible, or we conservatively block the reordering by enforcing  $(e_1, e_2) \in gb$ . The challenge is that the relation sc is heavily dependent on the specific execution. So how can we ascertain *syntactically* that a later event  $e_2$  cannot influence an earlier event  $e_1$ ?

One easily accessible syntactic property is the communication pattern between nodes (i.e. when one node performs a remote operation towards another).

Thus, to simplify the task, we over-approximate dependency (i.e. sc) with *communication*. Intuitively, if two nodes do not communicate in the network topology, then they cannot causally influence each other.

We write  $n_1 \iff n_2$  (defined below) to denote that nodes  $n_1$  and  $n_2$  communicate via some event in E, in that some thread t on  $n_1$  performs a remote operation  $e \in E$  towards  $n_2$ , written hasQP $(t, n_2, E)$ , or vice versa.

$$\begin{split} n_1 & \underset{E}{\longleftrightarrow} n_2 \triangleq \exists t. \; (n(t) = n_1 \land \mathsf{hasQP}(t, n_2, E)) \lor (n(t) = n_2 \land \mathsf{hasQP}(t, n_1, E)) \\ & \mathsf{hasQP}(t, \overline{n}, E) \triangleq \exists \mathsf{e} \in (E.\mathtt{nrW} \cup E.\mathtt{nrR}). \; t(\mathsf{e}) = t \land \overline{n}(\mathsf{e}) = \overline{n} \end{split}$$

We next show that if there is an sc-path from one event  $e_2$  to another  $e_1$  using public events in A, then the corresponding nodes (of the locations) of  $e_2$  and  $e_1$  must communicate via A. This is established in Lem. 1 below, with the proof given in Lem. 2.

**Lemma 1.** For all

$$A \subseteq E^{\mathsf{pub}}$$

, if  $\mathsf{e}_2 \xrightarrow{\mathsf{sc}|_A}^* \mathsf{e}_1$  then  $n(\mathsf{loc}(\mathsf{e}_2)) \leftrightsquigarrow^* n(\mathsf{loc}(\mathsf{e}_1))$ .

We are interested in the inverse direction of this lemma: a topological connection between the nodes (of the locations) of  $\mathbf{e}_2$  and  $\mathbf{e}_1$  is a necessary condition for an  $\mathbf{sc}$ -path from  $\mathbf{e}_2$  to  $\mathbf{e}_1$ . Put differently, if there is no communication between the nodes of  $\mathbf{e}_2$  and  $\mathbf{e}_1$ , then  $\mathbf{e}_2$  cannot influence  $\mathbf{e}_1$ . As such, we can use this to over-approximate safely whether an event can influence another. We conservatively assume that if the two nodes can communicate (outside of the thread) then  $\mathbf{e}_2$  might influence  $\mathbf{e}_1$ . These communications do not depend on a specific execution and can be ascertained syntactically from the pre-execution.

We can then prevent sc cycles across threads using the *fenced* condition below (Def. 8): for all  $e_1 \xrightarrow{po} e_2$  on public locations, if  $e_2$  might influence  $e_1$ , then we block the reordering. We subsequently prove that if a pre-execution is fenced, then it does not admit sc cycles across threads.

**Definition 8 (fenced).** A pre-execution

$$\langle E, \mathsf{po}, \mathsf{pf} \rangle$$

is fenced iff for all  $\mathsf{e}_1, \mathsf{e}_2 \in E^{\mathsf{pub}}$ , if  $\mathsf{e}_1 \stackrel{\mathsf{po}}{\longrightarrow} \mathsf{e}_2$  and  $n(\mathsf{loc}(\mathsf{e}_1)) \stackrel{\longleftrightarrow}{\longleftarrow} {}^* n(\mathsf{loc}(\mathsf{e}_2))$ , then  $(\mathsf{e}_1, \mathsf{e}_2) \in \mathsf{gb}$ .

**Theorem 4.** Given an RDMA<sup>SC</sup>-consistent execution  $\langle E, \mathsf{po}, \mathsf{pf}, \mathsf{rf}, \mathsf{mo}, \mathsf{nfo} \rangle$ , if its associated pre-execution  $\langle E, \mathsf{po}, \mathsf{pf} \rangle$  is fenced, then there is no sc cycle of the shape  $\mathsf{e}_1 \xrightarrow{\mathsf{po} \backslash \mathsf{ob}} \mathsf{e}_2 \xrightarrow{(\mathsf{sc}; [E^{\mathsf{pub}} \backslash t(\mathsf{e}_1)])^+; \mathsf{sc}} \mathsf{e}_1$  with  $\mathsf{e}_1, \mathsf{e}_2 \in E^{\mathsf{pub}}$ . That is, the second case of Theorem 2 does not arise.

**Robustness.** Lastly, we show that LDRF and fenced imply robustness under RDMA<sup>SC</sup>. Thus, this approach can be used to prevent RDMA weak behaviours.

**Theorem 5 (Robustness under RDMA<sup>SC</sup>).** Given a pre-execution  $\mathcal{G} = \langle E, po, pf \rangle$ , if  $\mathcal{G}$  is locally data-race free (Def. 7) and fenced (Def. 8), then  $\mathcal{G}$  is also robust under RDMA<sup>SC</sup> (Def. 5).

Fig. 6: Examples illustrating the limitation of Theorem 5, where the programs in (a) and (b) are robust (the weak behaviour a=1 is not allowed in either) while that in (c) is not robust (it admits the weak behaviour a=1); while Theorem 5 rightfully identifies (a) as robust (true positive) and (c) as not robust (true negative), it conservatively deems (b) not robust (false negative).

#### 4.3 Usage and Limitations

Local data-race freedom (Def. 7) and fenced (Def. 8) are intuitive properties that can be checked syntactically. Indeed, given a program, it is straightforward to check mechanically whether these properties hold or to provide an explicit counterexample and a suggested fix using the definition of gb (Def. 6). As a result, sufficient constraints can automatically be added to ensure robustness.

However, this simplicity can occasionally be the limitation of our approach. Specifically, as the main theorem does not account for interactions between threads, it takes a conservative approach, which at times can lead to false negatives (where the program is deemed not robust even though no weak behaviours are possible), recommending unnecessary restrictions.

To see this, consider the example in Fig. 6a, where  $a := x^2$  and  $y^3 := 1$  can be reordered *without* introducing weak behaviours. In this case, Theorem 5 rightfully confirms that no additional restrictions are necessary. By contrast, consider the variant shown in Fig. 6b: although the two extended threads do not introduce any additional weak behaviours, our approach assumes there might be a causal dependency from  $y^3 := 1$  to  $a := x^2$ , as is the case e.g. in Fig. 6c. As such, Theorem 5 cannot determine Fig. 6b as robust, and our approach would recommend inserting a poll operation in the first thread. Note that removing any of the six operations would enable Theorem 5 to ascertain Fig. 6b as robust.

Understanding that the reordering of the instructions in the first thread of Fig. 6b is not problematic would require a more complex static analysis beyond the scope of this paper.

# 5 Application: Tree Topology

Theorem 5 outlines the conditions under which we can guarantee that a program is robust under RDMA<sup>SC</sup>. However, while the LDRF property (Def. 7) is reasonable, the fenced property (Def. 8) can lead to excessive restrictions (e.g. as in Fig. 6). Specifically, for every pair of events  $(e_1, e_2)$  in program order, we must either verify that  $e_2$  cannot affect  $e_1$ , or ensure that their execution order is preserved. The main issue is that preserving the order of every pair of events can be particularly costly, notably when considering NIC remote write events. In

such cases, the only resort is to introduce a 'dummy' get operation and poll it, which is inefficient. Instead, we propose a strategy whereby we stipulate certain conditions on the network *topology* (i.e. the shape of the RDMA network) so that later events are often unable to influence earlier events.

To this end, we propose a *tree topology* that balances generality (supporting a wide range of programs) with efficiency and restrictiveness (requiring minimal additional constraints to respect the fenced property). In §5.1 we present an overview of our new set of restrictions and illustrate their rationale through examples. In §5.2 we formalises these restrictions and prove that they indeed imply robustness under RDMA<sup>sc</sup>. Finally, in §5.3 we demonstrate specific applications of the tree topology and how RDMA programs can make use of them.

#### 5.1 Overview of the Restrictions

We describe four different conditions that, if satisfied, ensure the robustness of RDMA programs under RDMA<sup>SC</sup>, and we justify them through examples.

**LDRF.** As before, we require that programs satisfy LDRF (Def. 7). As discussed, this is considered standard practice when writing RDMA programs and should not be seen as a limitation.

**Private Copies.** We require the *local locations* of RDMA operations – e.g. location y in  $y:=x^2$  – to be private (i.e. accessed by only one thread, namely that executing the RDMA operation). Intuitively, to maximise the efficiency of RDMA programs, we should ideally allow arbitrary interleaving of RDMA operations and CPU computations. For instance, let us consider the single-threaded program  $\mathsf{C} \triangleq y := x^2; \mathsf{c}^{\sharp}_{\mathsf{cpu}}$ , where  $\mathsf{c}^{\sharp}_{\mathsf{cpu}}$  denotes a block of CPU instructions that does not access location y. If y is private, then although  $\mathsf{c}^{\sharp}_{\mathsf{cpu}}$  and the get  $y := x^2$  may be reordered, this reordering will not lead to any observable weak behaviours. That is, when we run  $\mathsf{C}$  concurrently with any RDMA program  $\mathsf{C}'$  (i.e. as  $\mathsf{C}||\mathsf{C}'|$ ), if y is private, then we do not need to poll  $y := x^2$  before proceeding with  $\mathsf{c}^{\sharp}_{\mathsf{cpu}}$  (even though they may be reordered), as the reordering cannot be observed by  $\mathsf{C}'$ .

However, if y is accessible by other threads (on the same node or from a remote node), then the reordering becomes visible, allowing additional, potentially unwanted, weak behaviours. This is illustrated in the example below, where  $c_{\text{CDU}}^{\text{y}} \triangleq z := 1$  and y is public (accessed by nodes 1 and 3).

| y, z = 0                   | x = 1 |            |  |  |  |

|----------------------------|-------|------------|--|--|--|

| $y := x^2$                 |       | $a := z^1$ |  |  |  |

| z := 1                     |       | poll(1)    |  |  |  |

|                            |       | $b := y^1$ |  |  |  |

| $(a,b) = (1,0) \checkmark$ |       |            |  |  |  |

More concretely, due to the reordering, the later CPU computation (z := 1) can be observed before the earlier get  $(y := x^2)$ , leading to the weak outcome (a, b) = (1, 0).

Therefore, to prevent such weak behaviours, we stipulate that local locations of RDMA operations be private. This is not a costly limitation. Specifically, in the case of put operations, the data can easily be copied beforehand to a

one-time-use private location. In the case of get operations, it means the thread running the command needs to acknowledge the data and copy it to make it available to other threads having access to the node.

**Get in Order.** We stipulate that each get operation be followed by a remote fence. Recall that only certain reorderings are allowed on the operations of the same queue pair. Intuitively, put operations cannot be overtaken, and we do not need to restrict their usage. However, get operations can be overtaken by other get/put operations, as shown in the examples below, where the  $a:=x^2$  is overtaken by a later remote operation on the same queue pair, leading to weak behaviours.

|                       | x = 0                |                       | x, y = 0 |

|-----------------------|----------------------|-----------------------|----------|

| $a := x^2$ $b := x^2$ | x := 1               | $a := x^2$ $y^2 := 1$ | x := y   |

| (a, b) =              | $(1,0)$ $\checkmark$ | a =                   | 1 🗸      |

As such, to prevent non-SC behaviours, we require that each get operation be followed by a remote fence, forcing the queue pair to await the completion of the get before starting the next remote operation. Of course, if the get is polled before another RDMA operation is submitted, the remote fence is not needed. Note that since remote fences do not block CPU computations nor communications with other nodes, they are not very expensive and are a reasonable cost to pay to ensure remote operations towards a specific remote node stay in order.