# Semantics of Remote Direct Memory Access: Operational and Declarative Models of RDMA on TSO Architectures

GUILLAUME AMBAL\*, Imperial College London, UK BRIJESH DONGOL, University of Surrey, UK HAGGAI ERAN, NVIDIA, Israel VASILEIOS KLIMIS, Queen Mary University of London, UK ORI LAHAV, Tel Aviv University, Israel AZALEA RAAD, Imperial College London, UK

Remote direct memory access (RDMA) is a modern technology enabling networked machines to exchange information without involving the operating system of either side, and thus significantly speeding up data transfer in computer clusters. While RDMA is extensively used in practice and studied in various research papers, a formal underlying model specifying the allowed behaviours of concurrent RDMA programs running in modern multicore architectures is still missing. This paper aims to close this gap and provide semantic foundations of RDMA on x86-TSO machines. We propose three equivalent formal models, two operational models in different levels of abstraction and one declarative model, and prove that the three characterisations are equivalent. To gain confidence in the proposed semantics, the more concrete operational model has been reviewed by NVIDIA experts, a major vendor of RDMA systems, and we have empirically validated the declarative formalisation on various subtle litmus tests by extensive testing. We believe that this work is a necessary initial step for formally addressing RDMA-based systems by proposing language-level models, verifying their mapping to hardware, and developing reasoning techniques for concurrent RDMA programs.

CCS Concepts: • Software and its engineering  $\rightarrow$  Formal language definitions; • Theory of computation  $\rightarrow$  Program semantics; Distributed computing models; • Hardware  $\rightarrow$  Testing with distributed and parallel systems.

Additional Key Words and Phrases: RDMA, Operational Semantics, Declarative Semantics, x86-TSO

#### **ACM Reference Format:**

Guillaume Ambal, Brijesh Dongol, Haggai Eran, Vasileios Klimis, Ori Lahav, and Azalea Raad. 2024. Semantics of Remote Direct Memory Access: Operational and Declarative Models of RDMA on TSO Architectures. *Proc. ACM Program. Lang.* 8, OOPSLA2, Article 341 (October 2024), 68 pages. https://doi.org/10.1145/3689781

#### 1 Introduction

Remote direct memory access (RDMA) technologies such as *InfiniBand* and *RDMA* over Converged Ethernet (RoCE) enable a machine to have direct read/write access to the memory of another machine over a network, bypassing the operating systems of both machines. This way, remote reads and writes are performed with far fewer CPU cycles, leading to high-throughput, low-latency

Authors' Contact Information: Guillaume Ambal, Imperial College London, UK, g.ambal@imperial.ac.uk; Brijesh Dongol, University of Surrey , UK, b.dongol@surrey.ac.uk; Haggai Eran, NVIDIA, Israel, haggaie@nvidia.com; Vasileios Klimis, Queen Mary University of London, UK, v.klimis@qmul.ac.uk; Ori Lahav, Tel Aviv University, Israel, orilahav@tau.ac.il; Azalea Raad, Imperial College London, UK, azalea.raad@imperial.ac.uk.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. Copyrights for third-party components of this work must be honored. For all other uses, contact the owner/author(s).

ACM 2475-1421/2024/10-ART341

https://doi.org/10.1145/3689781

<sup>\*</sup>Corresponding author

networking, which is especially useful in massively parallel computer clusters, e.g. for data centres, big data, and scientific computation. Thanks to implementations that offer higher performance at a comparable cost over traditional networking infrastructure (e.g. TCP/IP sockets) [Gerstenberger et al. 2018], RDMA has achieved widespread adoption as of 2018 [Shpiner et al. 2017] and has been rapidly adopted in modern data centres.

At the lowest level, RDMA networks directly interact with the hardware through calls to read (get) and write (put) operations to remote memory locations. As a result, programming RDMA systems is conceptually similar to shared memory systems of existing hardware architectures such as Intel-x86 or ARM. A key difference, however, is that when a machine encounters a remote operation, the CPU forwards it onto the *network interface card* (NIC), which subsequently handles the remote operation and its associated memory accesses without further CPU involvement.

There is a wide range of RDMA implementations, starting from the Virtual Interface Architecture (VIA) [Dunning et al. 1998], later adapted by InfiniBand [IBTA 2022] and RoCE [InfiniBand Trade Association (IBTA) 2018]. Other standards include iWarp [Recio et al. 2007] and Omni-Path [Birrittella et al. 2015]. Some transfer technologies without NICs, such as FireWire [Anderson 1999], can also be considered RDMA, but they do not scale to wide networks. In most implementations, an RDMA NIC implements the transport in hardware and is controlled by software through APIs such as Verbs [linux-rdma 2018] or libfabric [OpenFabrics 2016]. A NIC typically connects to the host CPU through an internal server fabric such as PCIe, though in some cases the NIC and compute cores can be more tightly integrated, e.g. in academic proposals [Novakovic et al. 2014] and in DPUs [NVIDIA Corporation 2021]. In addition, there have been proposals for next-gen fabrics to replace PCIe (e.g. CXL [Van Doren 2019]).

Our focus here is on the IB Verbs model defined by IBTA [2022], using PCIe as the internal fabric. It was designed for InfiniBand and reused for RoCE, the two most popular RDMA technologies. While the specification for the iWarp protocol is slightly more permissive, its main implementation (libfabric) follows the stronger semantics presented here. Lastly, the more recent Omni-Path fabric also has legacy support for IB Verbs.

The performance gains of RDMA, as well as its wide range of implementations, have led to a surge of both theoretical and practical RDMA research [Aguilera et al. 2019; Dan et al. 2016; Wei et al. 2015; Zhu et al. 2015]. However, as we discuss below, programming RDMA systems *correctly* is not straightforward, and the RDMA community would benefit greatly from formal models and rigorous techniques for reasoning about RDMA programs.

A key challenge lies in understanding the different degrees of concurrency and their interaction thereof. More concretely, a program may comprise threads that run over multiple nodes (machines) over the network (inter-node concurrency), with each node itself executing several threads (intra-node concurrency). As such, to understand the behaviour of a concurrent RDMA program, one must understand how remote and local operations on different nodes interact with one another. The problem is that local operations are handled by the CPU, while remote operations are handled by the NIC independently and in *parallel* to other CPU operations. Consequently, two sequential operations may not be executed in the intended (program) order, leading to surprising outcomes.

To understand the behaviour of RDMA programs, we must understand the order in which CPU and remote operations are executed, how they may be *reordered*, and how and when their effects are made visible to concurrent threads, be they on the same or different nodes. Specifically, much in the same way that the semantics of multi-processor hardware architectures such as Intel-x86, POWER, and ARM have been described via *formal consistency models* (a.k.a. *memory models*) [Alglave et al. 2021, 2014; Cho et al. 2021; Mador-Haim et al. 2012; Pulte et al. 2018, 2019; Raad et al. 2022; Raad and Vafeiadis 2018; Raad et al. 2020b, 2019b; Sarkar et al. 2011; Sewell et al. 2010], we should ideally describe the semantics of RDMA programs *formally*. Such formal models not only provide a rigorous

underpinning for reasoning about the behaviour of programs, they have also been historically successful at identifying mistakes and ambiguities in the existing hardware reference manuals, as well as compilation bugs [Alglave et al. 2021, 2014; Lahav et al. 2017; Pulte et al. 2018; Raad et al. 2020b].

Unfortunately, the existing literature includes next to no work on the formal semantics of RDMA programs. Indeed, to our knowledge, the coreRMA model by Dan et al. [2016] is the only one to offer a formal description of RDMA programs. However, this work has four key shortcomings.

First, coreRMA assumes that CPU concurrency on each node is governed by the *sequential consistency* (SC) [Lamport 1979] model. This is an unrealistic assumption as no existing CPU architecture supports SC by default, and the two mainstream CPU architectures, Intel-x86 and ARM, are both subject to weaker models that exhibit behaviours not possible under SC. This is a significant gap since Intel-x86 and ARM architectures are ubiquitous.

Second, coreRMA describes the semantics *only declaratively* (i.e. via execution graphs that are subject to a set of axioms stipulating the absence of certain cycles in the graphs) and *not operationally* (via transitions that describe how the underlying hardware processes each operation and manipulates the memory). While declarative models are common in the literature of weak memory models and are more concise, operational models provide a more intuitive account of the hardware guarantees (as they prescribe a step-by-step mechanism for producing the behaviours of a program). Moreover, having two characterisations is useful not only for ensuring the accuracy of the formalism, but also because each formulation may be more useful for establishing different results. In particular, operational models are better suited for underpinning program logics and checking the reachability of an erroneous configuration and/or robustness for finite-state programs with loops (e.g. [Abdulla et al. 2021; Bouajjani et al. 2013; Lahav and Boker 2020]).

Third, the coreRMA authors have failed to *validate* their model against existing implementations in that they could not observe *any* of the weak behaviours allowed by coreRMA on existing implementations. That is, they could not practically justify the weakness of coreRMA.

Fourth and most importantly, as we discuss in detail in §6, coreRMA is not faithful to the RDMA specification [IBTA 2022] and departs from it in three different ways. In particular, coreRMA is neither stronger nor weaker than the specification, meaning that it admits certain behaviours disallowed by the specification, while prohibiting others allowed by the specification.

To close these gaps, we present RDMA<sup>TSO</sup>, the *first* formal semantics of RDMA programs in the context of the x86 architecture, which implements the TSO model [Sewell et al. 2010]. We describe RDMA<sup>TSO</sup> both *operationally* and *declaratively* and prove that the two are *equivalent*. Specifically, we first develop *two operational models* of RDMA<sup>TSO</sup>: (1) a *concrete* model, reflecting the hardware structure for propagating data across the network; and (2) a *simplified* model, abstracting away the hardware details, resulting in a cleaner model. We prove that our two operational characterisations of RDMA<sup>TSO</sup> are equivalent and mechanise our proof in Coq. We then present a declarative model of RDMA<sup>TSO</sup> and show that it is equivalent to our simplified (and thus also concrete) operational model.

We have developed RDMA<sup>TSO</sup> in close collaboration with engineers at NVIDIA, the largest manufacturer of networking products worldwide (after acquiring Mellanox in 2019). In particular, we have discussed all weak behaviours admitted by RDMA<sup>TSO</sup> with the engineers and have reflected the hardware justification for such behaviours in our concrete semantics. To further increase confidence in the fidelity of RDMA<sup>TSO</sup> to the specification, we have *empirically validated* it via extensive testing on existing implementations. More specifically, through our empirical validation we have managed to establish that (1) RDMA<sup>TSO</sup> is *not too strong*: we did not observe any of the behaviours prohibited by RDMA<sup>TSO</sup> on existing implementations; and (2) RDMA<sup>TSO</sup> is not *too weak*: we managed to observe *almost all* weak behaviours allowed by RDMA<sup>TSO</sup>, on existing implementations, and in the few cases where we did not observe a weak behaviour allowed by RDMA<sup>TSO</sup>, the engineers at NVIDIA

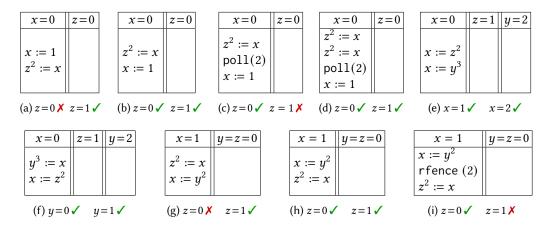

Fig. 1. TSO litmus tests for CPU concurrency, where locations x, y are accessed by all threads, while locations a, b are accessed by one thread only, and x = y = 0 on the first line denotes that x, y initially hold value 0.

confirmed that current implementations explicitly do not utilise the weakness admitted by the RDMA specification (see §5).

**Contributions and Outline.** In §2 we present an intuitive account of RDMA<sup>TSO</sup> through a number of examples. In §3 we present our concrete and simplified operational semantics of RDMA<sup>TSO</sup> and show that they are equivalent. In §4 we present our declarative semantics of RDMA<sup>TSO</sup> and show that it is equivalent to our simplified operational semantics. In §5 we describe how we empirically validated RDMA<sup>TSO</sup> through extensive litmus testing. We discuss related and future work in §6.

**Additional Material**. The full proofs of all stated theorems are given in the accompanying appendix and Coq development [Ambal et al. 2024]. We provide the executable RDMA code (in machine-readable format) and detailed instructions for replicating our experiments and analysing our litmus tests [Ambal et al. 2024].

#### 2 Overview

We present an account of the formal RDMA semantics, RDMA<sup>TSO</sup>, through a number of examples. We model concurrent programs running over a network of machines, and hereafter refer to each machine on the network as a *node*. In our setting, the semantics of a concurrent program and thus its possible weak behaviours are determined by two factors: (1) the *origin* of the threads, i.e. whether all threads originate from (are forked by) the same node and thus the concurrency is *intra-node* (within one node), or they originate from several nodes and thus concurrency is *inter-node* (across two or mode nodes); and (2) the *memory* targeted by the threads, i.e. whether each thread accesses its own local memory (on the same node), that of other nodes, or a combination thereof.

**Litmus Test Outcome Notation**. In the remainder of this article, as well as in the technical appendix, we present small representative examples (known as litmus tests in the literature) to illustrate whether an outcome is allowed by a given model (e.g. in Fig. 1, Fig. 2 and Fig. 3), and annotate a given outcomes with: (1)  $\checkmark$ , to denote that the outcome is *allowed* by the model *and observed* in practice (in our empirical validation); (2)  $\checkmark$ \*, to denote that the outcome is *allowed* by the model *and not observed* in practice; (3)  $\checkmark$ , to denote that the outcome is *disallowed* by the model *and not observed* in practice. See §5 or §A for more details.

**CPU Concurrency and TSO**. Existing work on RDMA semantics [Dan et al. 2016] assumes that CPU concurrency on each node is governed by the strong and unrealistic *sequential consistency* (SC) model [Lamport 1979]. We relax this assumption here and instead model each node as an x86 machine, subject to the TSO memory model [Sewell et al. 2010] introduced by the SPARC architecture [SPARC 1992]. Under TSO, a later read (in program order) can be reordered before an earlier write on a different location. This is illustrated in the *store buffering* example of Fig. 1a, where *x* and *y* denote locations accessed by both threads, while *a* and *b* denote locations accessed by

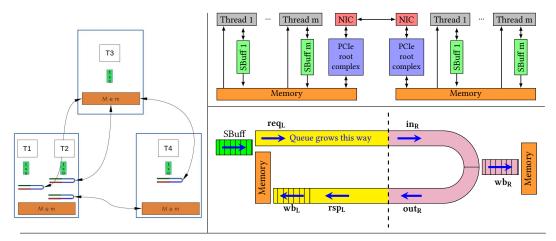

Fig. 2. Sequential RDMA litmus tests (excerpt), where each column (separated by ||) denotes a distinct node, the statement on the top line of each column denotes the initial values of locations, and the statements in the caption express whether each outcome is allowed by RDMA<sup>TSO</sup> and observed in practice ( $\checkmark$ ), or disallowed by RDMA<sup>TSO</sup> and not observed in practice ( $\checkmark$ ); i.e. we have empirically validated all outcomes shown.

one thread only. Specifically, the reads a := y and b := x can respectively be reordered before the writes x := 1 and y := 1, allowing them to read the initial value 0 from y and x, yielding a = b = 0 at the end of execution. Note that this weak behaviour is not allowed under the stronger SC model as SC admits no instruction reordering.

To prevent such write-read reordering, one can use an mfence as in Fig. 1b: mfence instructions cannot be reordered in either direction, and thus the weak behaviour shown is no longer possible. Indeed, other than write-read reordering, TSO admits no other reorderings and thus other weak behaviours, e.g. *load buffering* in Fig. 1c and *message passing* in Fig. 1d are prohibited under TSO.

**Remote Direct Memory Access (RDMA)**. RDMA allows one to build a network of communicating nodes (machines), where each node can *directly* access remote memory (of other nodes) through its network interface card (NIC). RDMA networks are programmed via operations that read from and write to remote memory, as well as various synchronisation operations. As such, programming RDMA networks is conceptually similar to shared memory systems such as TSO.

**Sequential (Single-Threaded) RDMA**<sup>TSO</sup> **Behaviours**. When a thread issues a put or get operation, it is handled by the NIC subsystem (and its associated queue pairs and buffers as shown

<sup>&</sup>lt;sup>1</sup>In our general model, all memory locations are shared and thus can be accessed by all threads both locally (on the same node) and remotely. However, for better readability, we follow the convention of naming locations accessed by multiple threads (locally or remotely) as x, y, z and w, while naming locations accessed by a single local thread as a, b, c and d.

in Fig. 4), in contrast to the CPU operations which are handled by the processor subsystem (and its associated store buffers). As such, the interaction between CPU and remote operations lead to further behaviours even within a *sequential* (single-threaded) program. We demonstrate this in the examples of Fig. 2, where each column represents a distinct node, numbered from 1 onwards. For instance, the example in Fig. 2a comprises a single thread on node 1 (the left-most column) that writes to the local location x (x := 1) and puts x towards the remote location z on node 2 ( $z^2 := x$ ).

Intuitively, when a thread t on n issues remote operations towards node  $\overline{n}$ , one can view these remote operations as if being executed by a thread running *in parallel* to t. As such, when a remote operation *follows* a CPU one, the order of the two operations is preserved since the parallel thread is spawned only after the CPU operation is executed. This is illustrated in Fig. 2a: as  $z^2 := x$  follows x := 1, it observes the x := 1 write and thus puts value 1 to x := 1; i.e. outcome x := 1 is not permitted.

By contrast, when a remote operation *precedes* a CPU one, the remote operation is performed by a 'separate thread' run in parallel to the later CPU operation in the main thread, and thus may execute before or after the CPU operation, meaning that in the latter case the execution order is not preserved. This is illustrated in Fig. 2b, where the earlier  $z^2 := x$  may execute (be reordered) after the later x := 1, and thus both z = 0 and z = 1 outcomes are possible.

Therefore, before using the result of a get or reusing the memory location of a put, it may be desirable to avoid such reordering and to wait for the remote operation to complete. This can be done through a CPU *poll* operation, poll(n), that blocks until the *earliest* (in program order) remote operation towards node n has completed. This is shown in Fig. 2c, obtained from Fig. 2b by inserting a poll after the remote operation: poll(2) waits for  $z^2 := x$  to complete before proceeding with x := 1, and thus  $z^2 := x$  can no longer be reordered after x := 1, prohibiting the x = 1 outcome.

Note that each poll(n) waits for *only one* (the earliest in program order) and *not all* pending remote operation towards n to complete. This allows for more efficient and fine-grained control over remote operations, but requires some care. For instance, consider the example in Fig. 2d, where poll(2) blocks until the *first*  $z^2 := x$  is complete, and thus the second  $z^2 := x$  operation can be reordered after the later x := 1, once again allowing for the z = 1 outcome.

Two remote operations towards *different* nodes are fully independent and can execute in either order (as if within two separate threads). For instance, the two get operations in Fig. 2e can execute in either order, and thus the final value of x may be either that of z (x = 1 outcome) or that of y (the x = 2 outcome). Similarly, Fig. 2f has two possible outcomes. The only way to enforce the execution order is polling the first remote operation before running the second.

The ordering guarantees on remote operations towards the *same* node are stronger and only certain reorderings are allowed. Recall that a remote (NIC) put operation  $x^n := y$  comprises two steps: a NIC local read (obtaining the value of y) and a NIC remote write (writing the value of y to  $x^n$ ). Similarly, a remote get operation  $x := y^n$  comprises two steps: a NIC remote read (obtaining the value of  $y^n$ ) and a NIC local write (writing the value of  $y^n$  to x). Intuitively, for remote operations on a given location x, these four steps mandate a *precedence* which in turn determines whether they can be reordered. Specifically, the four steps described above give way to the following precedence order: i) NIC local read; ii) NIC remote write; iii) NIC remote read; iv) NIC local write.

If a step with a higher precedence (e.g. a NIC local read) is in program order before one with a lower precedence (e.g. a NIC local write), then their order is preserved and they cannot be reordered; otherwise the order is not necessarily preserved and these steps can be reordered. For instance, in the Fig. 2g example, the earlier NIC local read on x (in  $z^2 := x$ ) has a higher precedence than the

$<sup>^{2}</sup>$ In the Verbs API, poll(n) returns a value denoting whether the operation being polled has completed and does not block the execution. However, it is common practice for calls to poll to be placed in a spin loop that returns only when the operation is completed, hence blocking the execution. Here, we model this common pattern with stronger behaviours.

| y=0   $x=0$   $x=0$ | $\begin{vmatrix} x=0 & y=0 \\ a:=y^2 & b:=x^1 \\ x:=1 & y:=1 \end{vmatrix}$ | $x=0$ $y=0$ $a := y^2$ $b := x^1$ $pol1(2)$ $pol1(1)$ $x := 1$ $y := 1$ | $y=0$ $x=0$ $x^2 := 1$ $y^1 := 1$ $poll(2)$ $poll(1)$ $a := y$ $b := x$ | $ \begin{array}{ c c c c c } \hline y{=}w{=}0 & x{=}z{=}0 \\ \hline x^2 := 1 & y^1 := 1 \\ c := z^2 & d := w^1 \\ poll(2) & poll(1) \\ poll(2) & poll(1) \\ a := y & b := x \\ \hline \end{array} $ |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-------------------------------------------------------------------------|-------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (a) $a=b=0$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | (b) $a=b=1$                                                                 | (c) $a=b=1$ X                                                           | (d) $a = b = 0 \checkmark$ *                                            | (e) $a = b = 0 \times$                                                                                                                                                                              |

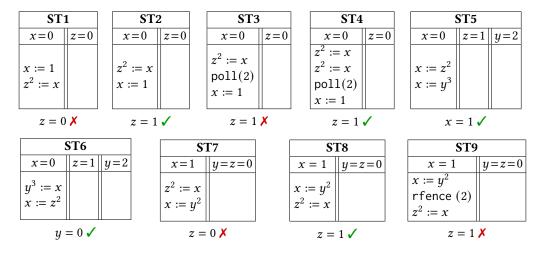

Fig. 3. Concurrent RDMA litmus tests (excerpt). The annotations in the captions indicate the given outcome is allowed by RDMA<sup>TSO</sup> and observed in our empirical validation ( $\checkmark$ ), allowed by RDMA<sup>TSO</sup> and not observable in practice ( $\checkmark$ \*), or disallowed by RDMA<sup>TSO</sup> and not observed in our validation ( $\checkmark$ ). That is, we have empirically validated all outcomes shown, except that in (d), which is due to the underlying implementation explicitly not utilising the weakness admitted by the specification – see §5 or §A for more details.

later NIC local write on x (in  $x := y^2$ ), and thus the order of these steps on x is preserved; i.e. the old value (1) of x is written to  $z^2$  leading to the z = 1 outcome, and the z = 0 outcome is disallowed.

By contrast, in the Fig. 2h example, the earlier NIC local write on x (in  $x := y^2$ ) has a lower precedence than the later NIC local read on x (in  $z^2 := x$ ) and thus the two steps can be reordered. Besides the SC outcome (z = 0), the program might execute the NIC local read on x before the NIC local write on x, thereby reading the initial value 1 from x and writing it to z (outcome z = 1).

As before, the reordering of the two remote operations in Fig. 2h can be prevented by polling the first operation before the second operation. However, polling is costly as it leads to global blocking: it blocks the current thread *both* on the CPU and the NIC towards *all* nodes (i.e. the current thread cannot execute any remote operations on *any* node). Alternatively, we can use a *remote fence*<sup>3</sup> operation, rfence (n), that blocks the current thread *only* on the NIC and *only* towards node n. (i.e. the thread cannot execute any remote operations towards n, but can execute both on the CPU as well as on the NIC towards nodes other than n). This in turn ensures that earlier (in program order) remote operations by the thread towards n (those before the fence) are executed before later remote operations towards n (those after the fence). This is illustrated in Fig. 2i, obtained from Fig. 2h by inserting rfence (2) between the two remote operations towards node 2, thereby ensuring that they are executed in order, and thus z = 1 is no longer possible.

**Concurrent (Multi-threaded) RDMA**<sup>TSO</sup> **Behaviours**. The real power of RDMA comes from multiple programs running on different nodes. This introduces a wide range of weak behaviours, as we describe below. A network can comprise several nodes, each running several concurrent threads. Here, we focus on a few examples each with two nodes, with each node comprising a single thread.

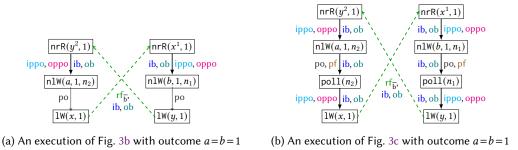

The store buffering behaviour due to the TSO model discussed in Fig. 1a is also possible in the RDMA setting, i.e. when locations x and y are on two different nodes, as shown in Fig. 3a. Moreover, further weak behaviours not possible under TSO, e.g. load buffering in Fig. 1c, are permitted in the RDMA setting, as shown in Fig. 3b. As before, this can be intuitively justified by conceptually viewing the remote operations in each thread as being executed by a separately spawned thread.

Most weak behaviours such as load buffering in Fig. 3b can be prevented by polling the remote operations as needed, as shown in Fig. 3c. Specifically, the poll operations in Fig. 3c await the completion of the preceding get operations, and thus the earlier get operations cannot be reordered after the later writes, thus prohibiting the weak behaviour a=b=1. However, a notable exception to this is the store buffering weak behaviour which cannot be prevented even when polling the

$<sup>^3</sup>$ For InfiniBand Verbs, this remote fence is not an independent operation but a flag that can be set on the later operation.

remote operations, as shown in Fig. 3d. This is because the specification of polling offers different guarantees for get and put operations. Specifically, polling a get operation  $a := x^2$  offers a strong guarantee and behaves intuitively: polling ensures that the get operation is complete (i.e. the value of  $x^2$  is fetched from node 2), and the executing thread performs the associated NIC local write on a before marking the operation as complete and proceeding with the remainder of the execution. By contrast, polling a put operation  $x^2 := 1$  offers a weaker guarantee: when sending value 1 towards node 2 to be put in  $x^2$ , the remote NIC merely acknowledges having received the data (value 1), but this data may still reside in a buffer (i.e. the PCIe fabric) of the remote node, pending to be written to the remote memory. Polling a put operation then simply awaits the acknowledgement of the data receipt and not its full completion (the data being written to memory). As such, it is possible to poll a put operation successfully before the associated remote write has fully completed. In the case of store buffering in Fig. 3d, it is possible for both poll operations to complete before the values of x and y are updated (to 1) in memory, and thus for the later reads to read their old values (0). However, note that existing implementations on current hardware (including ones against which we validated our model,) do not utilise this flexibility admitted by the specification. As such, the weak behaviour in Fig. 3d is not observable in practice, and thus we could not observe them in our validation effort (as indicated by ✓\*) – see §5. Nevertheless, since our aim is to capture the specification and not the implementation, we have modelled RDMATSO to allow this weak behaviour.

The behaviours discussed thus far all hold of the general RDMA specification [IBTA 2022] as well as the PCIe standard [PCI-SIG 2022]. However, in certain cases the PCIe standard offers stronger guarantees than those delineated by the RDMA specification. In particular, PCIe does not allow a read to fetch a pending value that has not yet been committed to memory. As such, a NIC remote read *flushes* (commits) all pending NIC remote writes to memory, while a NIC local read flushes all pending NIC local writes to memory. Interestingly, we can use this guarantee to prevent weak behaviours such as store buffering (which, in theory, cannot be prevented even via polling). Specifically, recall that polling a put only ensures that the data transmitted has reached the remote node and may not have yet been committed to its memory. However, by polling a later get (towards the same remote node) we can ensure the previous NIC remote writes (including that of the recently polled put) have been committed to the remote memory. An example of this is shown in Fig. 3e, obtained from Fig. 3d by adding additional gets ( $c := z^2$  and  $d := w^1$ ) and subsequently polling them. Reading from  $z^2$  and  $w^2$  in effect flushes the pending NIC remote writes on both nodes, ensuring that the effects of the earlier puts ( $x^2 := 1$  and  $y^1 := 1$ ) are committed to memory, which in turn ensures that the later a := y and b := x reads observe the updates on y and x (value 1), thus prohibiting a=b=0.

As mentioned above, this guarantee is PCIe-specific, and not mentioned by the RDMA standard. However, as PCIe is the *de facto* standard for RDMA programming, and since all widely available RDMA hardware is PCIe-compatible, here we opt to model this guarantee, resulting in a stronger model. Nevertheless, in §3 and §4 we also describe how we can weaken our models by removing this guarantee, both in our operational and declarative semantics.

Our aim here was to provide an overview of the weak RDMA behaviours both in the sequential and concurrent settings. We refer the reader to §A for further examples of weak behaviours.

# 3 RDMA<sup>TSO</sup> Concrete and Simplified Operational Semantics

We begin with several preliminary concepts. We present an informal account of our concrete semantics (§3.1), our formal concrete semantics (§3.2) and our equivalent simplified semantics (§3.3).

**Nodes and Threads**. We consider a system with N nodes (machines) and M threads in total across all machines. Let Node =  $\{1, ..., N\}$  be the set of *node identifiers*, and Tid =  $\{1, ..., M\}$  be

the set of *thread identifiers*. We use n and t to range over Node and Tid, respectively. Given a node n, we write  $\overline{n}$  to range over Node\  $\{n\}$ . Each thread  $t \in \mathsf{Tid}$  is associated with a node, written n(t). Note that multiple threads may run on the same node.

**Memory Locations**. Each node n has a set of *locations*,  $Loc_n$ , accessible by all nodes. We define  $Loc \triangleq \biguplus_n Loc_n$  and  $Loc_{\overline{n}} \triangleq Loc \setminus Loc_n$ . We use  $x^n, y^n, z^n$  and  $x^{\overline{n}}, y^{\overline{n}}, z^{\overline{n}}$  to range over  $Loc_n$  and  $Loc_{\overline{n}}$ , respectively. When the choice of n is clear, we write x for  $x^n$ ; similarly for  $\overline{n}$ . For clarity, we use distinct location names across nodes, and thus write n(x) for the unique  $n \in Node$  where  $x \in Loc_n$ .

**Values and Expressions**. We assume a set of values, Val, with  $\mathbb{N} \subseteq \text{Val}$ , and use v to range over Val. We assume a language of expressions over Val and Loc, and elide its exact syntax and semantics (as these are standard). We denote by Exp the set of all expressions and use e to range over Exp. We write [e] for the semantic evaluation of a *closed* expression e (i.e. one without any locations), elocs(e) for the locations in an expression e, and e[v/x] for the expression obtained from e after substituting all occurrences of e by e. We use  $e^n$  to range over expressions with elocs( $e^n$ )  $\subseteq \text{Loc}_n$ .

**Sequential Commands and Programs**. *Sequential* programs running on node n are described by the  $C^n$  grammar below and include primitive commands  $(c^n)$ , sequential composition  $(C_1^n; C_2^n)$ , non-deterministic choice  $(C_1^n + C_2^n)$ , executing either  $C_1^n$  or  $C_2^n$ ) and non-deterministic loops  $(C^{n*}, C_2^n)$ , executing  $C^n$  for a finite, possibly zero, number of iterations). A (concurrent) *program*, P, is a map from thread identifiers to commands, associating each thread  $t \in Tid$  with a command on node n(t).

```

\begin{array}{ll} \mathsf{Comm}\ni\mathsf{C}^n::=\mathsf{skip}\mid\mathsf{c}^n\mid\mathsf{C}_1^n;\mathsf{C}_2^n\mid\mathsf{C}_1^n+\mathsf{C}_2^n\mid\mathsf{C}^{n*} & \mathsf{PComm}\ni\mathsf{c}^n::=\mathsf{cc}^n\mid\mathsf{rc}^n \\ \mathsf{CComm}\ni\mathsf{cc}^n::=x:=e^n\mid\mathsf{assume}(x=v)\mid\mathsf{assume}(x\neq v)\mid\mathsf{mfence}\mid x:=\mathsf{CAS}(y,e_1,e_2)\mid\mathsf{poll}\;(\overline{n}) \\ \mathsf{RComm}\ni\mathsf{rc}^n::=x:=\overline{y}\mid\overline{y}:=x\mid\mathsf{rfence}\;(\overline{n}) \end{array}

```

Primitive commands include CPU ( $cc^n$ ) and RDMA ( $rc^n$ ) operations. A CPU operation on n may be a no-op (skip), an assignment to a local location (x := e), an assumption on the value of a local location (assume(x = v) and  $assume(x \neq v)$ ), a memory fence (mfence), an atomic CAS ('compare-and-set') operation ( $x := CAS(y, e_1, e_2)$ ), or a 'poll',  $poll(\overline{n})$ , that awaits the completion notification of the earliest put/get that is pending (not yet acknowledged). An RDMA operation may be (i) a 'get',  $x := \overline{y}$ , reading from remote location  $\overline{y}$  and writing the result to local location x; (ii) a 'put',  $\overline{y} := x$ , reading from local location x and writing the result to remote location  $\overline{y}$ ; or (iii) an 'RDMA fence',  $rfence(\overline{n})$ , which ensures that all later (in program order) RDMA operations towards  $\overline{n}$  will await the completion of all earlier RDMA operations towards  $\overline{n}$ . Note that poll ( $\overline{n}$ ) is executed by the CPU and blocks its thread (and prevents the requests of later remote operations), while  $rfence(\overline{n})$  blocks the NIC for the execution of remote operations towards node  $\overline{n}$ . In what follows, we write  $\overline{x} := 1$  as a shorthand for  $\overline{x} := a$  for some local location a containing value 1.

# 3.1 RDMA<sup>TSO</sup> Concrete Operational Semantics at a Glance

**RDMA**<sup>TSO</sup> **Architecture and CPU Operations**. Conceptually, the RDMA<sup>TSO</sup> architecture is as shown at the top-right of Fig. 4, where for brevity we depict two nodes, each comprising (1) m threads and their associated FIFO (first-in-first-out) *store buffers*; (2) a network interface card (NIC) and its PCIe root complex; and (3) the memory. Store buffers are used to model write-read reordering on TSO, which account for the weak behaviour in Fig. 1a. Specifically, executing a write on TSO comprises two steps: (i) when a thread issues a write, the write is only recorded in its store buffer; (ii) writes in the buffer are debuffered (in FIFO order) and propagated to the local memory at a later point. When a thread issues a read from a location x, it first consults its own store buffer. If it contains a write for x, the thread reads the value of the latest such write; otherwise, the thread reads the value of x from its local memory. In other words, one can model the reordering of a write w

Fig. 4. RDMA<sup>TSO</sup> architecture overview (top, right); a possible RDMA network configuration with three nodes and four thread (left); the queue-pair structure (below, right)

|                            | $y^{\overline{n}} := x^n$ | $y^{\overline{n}} := v$ | ack <sub>p</sub> | $x^n\coloneqq y^{\overline{n}}$ | $x^n := v$ | cn | rfence $\overline{n}$ |

|----------------------------|---------------------------|-------------------------|------------------|---------------------------------|------------|----|-----------------------|

| $b \in SBuff$              | ✓                         |                         |                  | ✓                               | ✓          |    | <b>✓</b>              |

| $req_L$                    | ✓                         |                         |                  | ✓                               |            |    | ✓                     |

| $in_R$                     |                           | ✓                       |                  | ✓                               |            |    |                       |

| $\mathbf{wb_R}$            |                           | ✓                       |                  |                                 |            |    |                       |

| $out_R$                    |                           |                         | ✓                | ✓                               | ✓          |    |                       |

| $rsp_L$                    |                           |                         | ✓                |                                 | ✓          |    |                       |

| $\mathbf{wb}_{\mathbf{L}}$ |                           |                         |                  |                                 | ✓          | ✓  |                       |

Fig. 5. The types of entries in the store buffers (b) of a thread on n and its six buffers on the  $\overline{n}$ -queue pair

after a later read r by *delaying* the debuffering of w until after r has executed. Moreover, executing an mfence or a CAS debuffers all its delayed writes in the store buffer and propagates them to memory (in FIFO order), thus preventing write-read reordering. That is, the only CPU operations that a store buffer contains are delayed writes. We describe the execution of polls shortly.

**Remote Operations and Queue Pairs**. To model the communication between the nodes, each thread t has a distinct *queue pair* for each remote node whose memory t accesses. For instance, the network configuration in the left of Fig. 4 comprises three nodes with four threads and with the queue pairs depicted as 'horse-shoes', where e.g. thread T2 in the bottom left node accesses the memories of the other two nodes, and it does so through two distinct queue pairs shown underneath T2. We refer to the queue pair of a thread towards node  $\overline{n}$  as its  $\overline{n}$ -queue pair.

The details of a queue-pair structure is shown at the bottom-right of Fig. 4, where each queue pair of thread t is connected to the store buffer of t. As shown, an  $\overline{n}$ -queue pair comprises six FIFO buffers— $\mathbf{req_L}$ ,  $\mathbf{in_R}$ ,  $\mathbf{wb_R}$ ,  $\mathbf{out_R}$ ,  $\mathbf{rsp_L}$ , and  $\mathbf{wb_L}$ —that we describe below. A queue pair contains pending operations if any of its  $\mathbf{in_R}$ ,  $\mathbf{out_R}$  or  $\mathbf{rsp_L}$  components is non-empty. The types of the entries in each of the six buffers of a queue pair is also summarised in Fig. 5.

Recall that a remote operation  $rc^n$  may either be a get, put or remote fence instruction. When t executes a remote operation  $rc^n$  towards node  $\overline{n}$ , it adds  $rc^n$  to its store buffer. That is, as well as CPU (delayed) writes, a store buffer may contain remote (get, put and fence) operations. Once  $rc^n$  is debuffered from the store buffer, it is forwarded to its  $\overline{n}$ -queue pair, where it travels through the queue-pair pipeline and is processed differently depending on the type of  $rc^n$ , as we describe below.

**Request Buffers (req**<sub>L</sub>). The **req**<sub>L</sub> is the entry point of the queue pair, containing remote requests that are to be forwarded. It comprises a sequence of remote get, put and fence operations to be handled by the local NIC. When an entry  $rc^n$  reaches the head of  $req_L$ , it is processed as follows. (1) If  $rc^n$  is a get, then it is simply forwarded to the remote inbox  $in_R$ . (2) If  $rc^n$  is a put  $x^{\overline{n}} := y$ , then the value v of v is looked up in the local memory and v is forwarded to v in v is replaced with its current in-memory value. (3) If v is a remote fence, then the execution on the queue pair is blocked until it has no pending operations, i.e. v in v and v and v are all empty.

**Inbox Buffers** ( $\mathbf{in_R}$ ). The  $\mathbf{in_R}$  contains requests forwarded by  $\mathbf{req_L}$  that are to be processed by  $\overline{n}$ , i.e. each  $\mathbf{req_L}$  entry is either a get or a put with a value (of the form  $y^{\overline{n}} := v$ ). Processing a put  $y^{\overline{n}} := v$  (once at  $\mathbf{in_R}$  head) forwards it to the remote write-back buffer  $\mathbf{wb_R}$  and also sends a *put acknowledgement*,  $\mathbf{ack_p}$ , to  $\mathbf{out_R}$ . Processing a get  $x := y^{\overline{n}}$  (once at  $\mathbf{in_R}$  head) does not immediately fetch the y value from the  $\overline{n}$  memory; rather, it forwards it to  $\mathbf{out_R}$  to be fulfilled later in  $\mathbf{out_R}$ .

**Outbox Buffers (out**<sub>R</sub>). The **out**<sub>R</sub> buffer contains requests processed or forwarded by  $in_R$ , and thus each entry in  $out_R$  is either a put acknowledgement (ack<sub>p</sub>), a get operation  $x := y^{\overline{n}}$  yet to be fulfilled, or a fulfilled get x := v. An acknowledgement or a fulfilled get is processed when it reaches the head of  $out_R$ , whereupon it is simply forwarded to  $rsp_L$ . By contrast, a yet-to-be-fulfilled get  $x := y^{\overline{n}}$  may be fulfilled at any time (before reaching the  $out_R$  head), where the value v of y is fetched from the memory of  $\overline{n}$ , and  $x := y^{\overline{n}}$  is transformed to the fulfilled get x := v and left in  $out_R$ . This fulfilled get is later processed once it reaches the head of  $out_R$ , as described above.

**Remote Write-Back Buffers (wb<sub>R</sub>).** The **wb**<sub>R</sub> buffer contains requests forwarded by **in**<sub>R</sub>, and thus each entry in **wb**<sub>R</sub> is a put operation with a value (of the form  $y^{\overline{n}} := v$ ). Processing  $y^{\overline{n}} := v$  (at the head of **wb**<sub>R</sub>) simply removes it from **wb**<sub>R</sub> and writes v to y in the memory of  $\overline{n}$ .

**Response Buffers** ( $rsp_L$ ). The  $rsp_L$  buffer contains processed requests forwarded by  $out_R$ , and thus each entry in  $rsp_L$  is either an  $ack_p$ , acknowledging a processed put, or a fulfilled get. Processing each  $rsp_L$  entry (once at the head of  $rsp_L$ ) generates a *completion notification*, cn, which is used to serve poll requests, as we describe shortly. Specifically, processing  $ack_p$  simply removes it from  $rsp_L$  and forwards a completion notification to  $wb_L$ . Analogously, processing a fulfilled get x := v simply forwards x := v together with a completion notification to  $wb_L$ .

**Local Write-Back Buffers** ( $\mathbf{w}\mathbf{b}_L$ ). The  $\mathbf{w}\mathbf{b}_L$  buffer contains processed requests forwarded by  $\mathbf{r}\mathbf{s}\mathbf{p}_L$ ; i.e. each entry in  $\mathbf{w}\mathbf{b}_L$  is either a completion notification (cn, associated with processed gets and puts), or a fulfilled get (of the form x := v). Processing a fulfilled get x := v simply removes it and writes v to x in the local memory. A completion notification is left in the  $\mathbf{w}\mathbf{b}_L$  and is only removed when the associated get/put operation is polled, as we describe below.

**Poll Operations**. Once a get enters  $\mathbf{req_L}$ , it progresses through the pipeline as follows.  $(G_1)$  it is forwarded to  $\mathbf{in_R}$ ;  $(G_2)$  it is forwarded to  $\mathbf{out_R}$  without being fulfilled;  $(G_3)$  it is fulfilled at some point while in  $\mathbf{out_R}$ ;  $(G_4)$  it is forwarded to  $\mathbf{rsp_L}$ ;  $(G_5)$  it is forwarded to  $\mathbf{wb_L}$  together with a completion notification  $(c_n)$ ; and  $(G_6)$  it is removed from  $\mathbf{wb_L}$  and its effect is written to memory.

Similarly, once a put operation  $x^{\overline{n}} := y$  enters the queue-pair pipeline it proceeds as follows. (P<sub>1</sub>) it is simplified to  $x^{\overline{n}} := v$  (where v is the value of y in the local memory) and forwarded to  $\mathbf{in}_R$ ; (P<sub>2</sub>) it is forwarded to  $\mathbf{wb}_R$  and simultaneously an acknowledgement  $\mathsf{ack}_p$  is forwarded to  $\mathbf{out}_R$ ; (P<sub>3</sub>) its  $\mathbf{wb}_R$  entry is eventually removed and applied to the remote memory; its associated  $\mathsf{ack}_p$  in  $\mathbf{out}_R$  (P<sub>4</sub>) is forwarded to  $\mathbf{rsp}_L$ ; and (P<sub>5</sub>) later forwarded to  $\mathbf{wb}_L$  as cn.

$<sup>^4</sup>$ In some implementations, write-back buffers ( $wb_L$  and  $wb_R$ ) of different queue pairs may physically use the same hardware buffers in the PCIe fabric. This does not introduce any additional weak behaviours.

Program transitions: Prog

$$\frac{\text{Lab} \uplus \{\varepsilon\}}{\text{Lab}_n} \text{ Prog } \frac{\text{Command transitions: Comm} \xrightarrow{\text{Lab} \uplus \{\varepsilon\}} \text{ Comm}}{\text{Lab}_n} \xrightarrow{\text{Lab}_n} \Rightarrow \begin{cases} 1 \mathbb{W}(x^n, v), 1 \mathbb{R}(x^n, v), CASS(x^n, v_1, v_2), CASF(x^n, v), & x, y \in \text{Loc}, \\ F, P(\overline{n}), \text{Get}(x^n, y^{\overline{n}}), \text{Put}(y^{\overline{n}}, x^n), \text{rF}(\overline{n}) & v, v_1, v_2 \in \text{Val} \end{cases}$$

$$\frac{C_1 \xrightarrow{l} C_1'}{C_1; C_2 \xrightarrow{l} C_1'; C_2} \xrightarrow{\text{skip}; C \xrightarrow{\varepsilon} C} \xrightarrow{c \xrightarrow{\varepsilon} C} \xrightarrow{t \in \{1, 2\}} \xrightarrow{C_1 + C_2 \xrightarrow{\varepsilon} C_1^n} \xrightarrow{C^* \xrightarrow{\varepsilon} \text{skip}} \xrightarrow{C^* \xrightarrow{\varepsilon} \text{skip}} \xrightarrow{C^* \xrightarrow{\varepsilon} C; C^*}$$

$$\frac{C \xrightarrow{\varepsilon} C'}{C \xrightarrow{\varepsilon} C'} \xrightarrow{\text{elocs}(e) = \emptyset} \xrightarrow{\text{elocs}(e) = \emptyset} \xrightarrow{\text{elocs}(e_{\text{old}}) = \text{elocs}(e_{\text{new}}) = \emptyset} \xrightarrow{z := \text{CAS}(x, e_{\text{old}}, e_{\text{new}})} \xrightarrow{CASF(x, v)} z := v$$

$$\frac{\text{elocs}(e_{\text{old}}) = \text{elocs}(e_{\text{new}}) = \emptyset}{z := \text{CAS}(x, e_{\text{old}}, e_{\text{new}})} \xrightarrow{CASF(x, v)} \xrightarrow{z := v} \xrightarrow{\text{get}(x, \overline{y})} \text{skip}$$

$$\frac{\overline{y} := x \xrightarrow{\text{Put}(\overline{y}, x)}}{\text{skip}} \xrightarrow{\text{skip}} \xrightarrow{rfence} \overline{n} \xrightarrow{rF(\overline{n})} \text{skip}} \xrightarrow{poll(\overline{n})} \xrightarrow{P(\overline{n})} \xrightarrow{\text{skip}} \xrightarrow{poll(\overline{n})} \xrightarrow{P(\overline{n})} \xrightarrow{\text{skip}} \xrightarrow{v \neq v'} \xrightarrow{\text{assume}(x = v)} \xrightarrow{1 \mathbb{R}(x, v)} \xrightarrow{\text{skip}} \xrightarrow{poll(\overline{n})} \xrightarrow{P(\overline{n})} \xrightarrow{\text{poll}(\overline{n})} \xrightarrow{P(\overline{n})} \xrightarrow{\text{poll}(\overline{n})} \xrightarrow{P(\overline{n})} \xrightarrow{\text{poll}(\overline{n})} \xrightarrow{P(\overline{n})} \xrightarrow{\text{poll}(\overline{n})} \xrightarrow{\text{poll}($$

Fig. 6. The RDMATSO program and command transitions

That is, both get and put operations result in a completion notification (cn) when complete. Indeed, this is precisely why we record an acknowledgement for each put: the ack<sub>p</sub> serves as a placeholder for a processed put, so that we can generate an associated notification when complete.

Recall that  $poll(\overline{n})$  awaits the completion of the earliest unpolled get/put towards  $\overline{n}$ . To achieve this, completion notifications are left in  $\mathbf{wb_L}$  until polled. Executing  $poll(\overline{n})$  can proceed if the head of  $\mathbf{wb_L}$  of the  $\overline{n}$ -queue pair is a cn entry, in which case this cn entry (the earliest in FIFO order) is removed. If  $\overline{n}$ - $\mathbf{wb_L}$  is empty or its head is a write entry, then the execution of  $poll(\overline{n})$  is blocked.

# 3.2 RDMA<sup>TSO</sup> Concrete Operational Semantics

We describe the RDMA<sup>TSO</sup> concrete operational semantics by separating the transitions of its program and hardware subsystems. The former describe the steps in program execution, e.g. how a branching program is reduced. The latter describe how the memory, store buffers and queue pairs evolve throughout the execution, e.g. how remote puts reach the memory. The RDMA<sup>TSO</sup> operational semantics is then defined by combining the transitions of its program and hardware subsystems.

**Program Transitions**. Program transitions in the middle of Fig. 6 are defined via the transitions of their constituent commands. Command transitions are of the form  $C \stackrel{l}{\rightarrow} C'$ , where  $C, C' \in C$  comm are sequential commands and l is a *label*. A label is either  $\varepsilon$  for silent transitions, or in Lab (defined at the top of Fig. 6) for executing a primitive command. Labels are defined as the union of Lab<sub>n</sub> for all nodes n. A label in Lab<sub>n</sub> may be (1)  $1 \mathbb{W}(x^n, v)$ , for a CPU write on location x with value v; (2)  $1 \mathbb{R}(x^n, v)$ , for a CPU read on x reading v; (3)  $CASS(x^n, v_1, v_2)$ , for a successful CAS reading the expected value  $v_1$  from x and updating it to  $v_2$ ; (4)  $CASF(x^n, v)$ , for a failed CAS where the expected

value does not match the value v of x in memory; (5) F, for a memory fence; (6)  $P(\overline{n})$ , for a poll on  $\overline{n}$ ; (7)  $Get(x^n, y^{\overline{n}})$ , for  $x^n := y^{\overline{n}}$ ; (8)  $Put(y^{\overline{n}}, x^n)$ , for  $y^{\overline{n}} := x^n$ ; or (9)  $rF(\overline{n})$ , for a remote fence on  $\overline{n}$ .

Command transitions for sequential composition, choice and loops (the top line) are standard. The next four transitions reduce assignments and CAS operations. As assignments and CAS involve expressions, their transitions rewrite expressions step-by-step, as defined at the bottom of Fig. 6 (via  $\leadsto$  transitions). Each rewrite step of assignment rewrites x := e as assume (y = v);  $x := e \lfloor v/y \rfloor$ , replacing a location y in e with an arbitrary value v and checking that v matches the value of v via assume transitions with memory ones. The two rewrite transitions for CAS are analogous. Observe that when v contains no locations, then it is reduced to skip with the corresponding CPU write label for writing the value of v via v then it is reduced to skip with the corresponding CPU write label for writing the value of v via v

Program transitions are of the form  $P \xrightarrow{t:l} P'$ , where P, P' denote (concurrent) programs, t is the identifier of the executing thread, and l is the transition label. Program transitions simply lift the transitions of their constituent threads (the bottom right rule).

**Hardware Transitions**. The RDMA<sup>TSO</sup> hardware transitions, given in the middle of Fig. 7, are of the form M, B, QP  $\xrightarrow{t:l}$  M', B', QP', where M, M' are global memories, B, B' are store-buffer maps and QP, QP' are queue-pair maps, defined at the top of Fig. 7. We model a memory as a map from locations to values. A store-buffer map is a function mapping each thread t to a store buffer on its associated node n(t). A store buffer b on node n is a sequence of CPU writes and RDMA puts, gets and fences, as described in §3.1 (see Fig. 5). A queue-pair map is a function mapping each thread t (on node n(t)) to another function associating each non-n(t) node with a queue pair. That is, each thread t is associated with a set of queue pairs, one for each other node on the network. A queue pair qp is a tuple of six buffers,  $\mathbf{req_L}$ ,  $\mathbf{in_R}$ ,  $\mathbf{wb_R}$ ,  $\mathbf{out_R}$ ,  $\mathbf{rsp_L}$  and  $\mathbf{wb_L}$ , as described in §3.1. Each queue-pair buffer in turn is a sequence of entries as prescribed in Fig. 5. We write 'qp.' to project components of qp and use a standard map update notation to modify these components.

The first five hardware transitions describe the execution of CPU operations, as described in §3.1. Specifically, when a thread writes v to x, it records this write in its store buffer (first transition). Recall that when a thread t reads from x, it first consults its own store buffer, followed by the memory if no write to x is found in the store buffer. This lookup chain is captured by  $M \triangleleft B(t)$  (second transition), defined below the hardware transitions in Fig. 7. The execution of a CAS or mfence proceeds if the store buffer of the executing thread is empty (the next three transitions).

The next transition describes the debuffering of a CPU write and propagating it to the memory. Similarly, the transition after describes debuffering a remote operation  $rc^n$  towards node  $\overline{n}$ , where it is removed from the store buffer and appended to the  $req_L$  component of the  $\overline{n}$ -queue pair.

The next three transitions describe executing a remote get, put or fence operation, where a corresponding entry is added to the store buffer. The penultimate transition describes executing a poll on  $\overline{n}$ , which removes the earliest completion notification in  $\mathbf{wb_L}$  of the  $\overline{n}$ -queue pair. The last transition describes how the queue-pair entries travel through its six buffers, captured by the queue-pair transitions ( $\rightarrow_{qp}$ ) defined at the bottom of Fig. 7 (ignoring highlights for now).

Recall from §3.1 that once a get operation enters a queue pair it travels through the queue-pair pipeline in six steps, i.e.  $G_1$ – $G_6$  on p. 11. This is captured by the top  $\rightarrow_{qp}$  transition at the bottom of Fig. 7, where for brevity we have combined these six steps into one transition with a disjunctive

```

M \in Mem \triangleq Loc \rightarrow Val B \in SBMap \triangleq \lambda t \in Tid.SBuff_{n(t)} QP \in QPMap \triangleq \lambda t.(\lambda \overline{n(t)}.QPair_{n}^{\overline{n}})

\mathsf{b} \in \mathsf{SBuff}_n \triangleq \left\{ x^n := v, y^{\overline{n}} := x^n, x^n := y^{\overline{n}}, \mathsf{rfence} \ \overline{n} \right\}^* \qquad \mathsf{qp} \in \mathsf{QPair}_n^{\overline{n}} \triangleq \mathsf{Req}_n^{\overline{n}} \times \mathsf{In}_n^{\overline{n}} \times \mathsf{WBR}_n^{\overline{n}} \times \mathsf{Out}_n^{\overline{n}} \times \mathsf{Rsp}_n^{\overline{n}} \times \mathsf{WBL}_n^{\overline{n}}

\operatorname{req_L} \in \operatorname{Req}_n^{\overline{n}} \triangleq \left\{ y^{\overline{n}} := x^n, x^n := y^{\overline{n}}, \operatorname{rfence} \, \overline{n} \right\}^* \quad \operatorname{in}_R \in \operatorname{In}_n^{\overline{n}} \triangleq \left\{ y^{\overline{n}} := v, x^n := y^{\overline{n}} \right\}^* \quad \operatorname{wb_L} \in \operatorname{WBL}_n^{\overline{n}} \triangleq \left\{ \operatorname{cn}, x^n := v \right\}^* = \operatorname{req}_R^{\overline{n}} = \operatorname{req}_R^{\overline{n}

\mathbf{out_R} \in \mathbf{Out_n^{\overline{n}}} \triangleq \left\{\mathsf{ack_p}, x^n := v, x^n := y^{\overline{n}}\right\}^* \qquad \mathbf{rsp_L} \in \mathsf{Rsp}_n^{\overline{n}} \triangleq \left\{\mathsf{ack_p}, x^n := v\right\}^* \qquad \mathbf{wb_R} \in \mathsf{WBR}_n^{\overline{n}} \triangleq \left\{y^{\overline{n}} := v\right\}^*

\frac{\mathsf{B}' = \mathsf{B}[t \mapsto (x := v) \cdot \mathsf{B}(t)]}{\mathsf{M}, \mathsf{B}, \mathsf{QP} \xrightarrow{t: \mathsf{LW}(x, v)} \mathsf{M}, \mathsf{B}', \mathsf{QP}} \xrightarrow{\mathsf{M}, \mathsf{B}, \mathsf{QP}} \frac{(\mathsf{M} \triangleleft \mathsf{B}(t))(x) = v}{\mathsf{M}, \mathsf{B}, \mathsf{QP}} \xrightarrow{\mathsf{M}, \mathsf{B}, \mathsf{QP}} \frac{\mathsf{B}(t) = \varepsilon}{\mathsf{M}, \mathsf{B}, \mathsf{QP}} \xrightarrow{\mathsf{M}(x) = v_1} \mathsf{M}[x \mapsto v_2], \mathsf{B}, \mathsf{QP}

\frac{\mathsf{B}(t) = \varepsilon \qquad \mathsf{M}(x) = v}{\mathsf{M}, \mathsf{B}, \mathsf{QP}} \qquad \frac{\mathsf{B}(t) = \varepsilon}{\mathsf{M}, \mathsf{B}, \mathsf{QP}} \qquad \frac{\mathsf{B}(t) = b \cdot (x := v)}{\mathsf{M}, \mathsf{B}, \mathsf{QP} \xrightarrow{t : \varepsilon} \mathsf{M}[x \mapsto v], \mathsf{B}[t \mapsto b], \mathsf{QP}}

\mathsf{B}(t) = \mathsf{b} \cdot \mathsf{rc}^n \qquad \mathsf{rc}^n \in \left\{ x := y^{\overline{n}}, y^{\overline{n}} := x, \mathsf{rfence} \ \overline{n} \right\} \qquad \mathsf{QP}(t)(\overline{n}) = \mathsf{qp} \qquad \mathsf{qp}' = \mathsf{qp}[\mathbf{req_L} \mapsto \mathsf{rc}^n \cdot \mathsf{qp}.\mathbf{req_L}]

M. B. OP \xrightarrow{t:\varepsilon} M. B[t \mapsto b]. OP[t \mapsto QP(t)[\overline{n} \mapsto qp']]

B' = B[t \mapsto (\overline{y} := x) \cdot B(t)] B' = B[t \mapsto (\text{rfence } \overline{n}) \cdot B(t)]

\mathsf{B}' = \mathsf{B}[t \mapsto (x := \overline{y}) \cdot \mathsf{B}(t)]

QP(t)(\overline{n}) = qp \qquad qp.\underline{\mathbf{wb_L} = \alpha \cdot \mathsf{cn}} \qquad qp' = qp[\underline{\mathbf{wb_L} \mapsto \alpha}] \qquad M, QP(t)(\overline{n}) \to_{qp} M', qp

M, B, QP \xrightarrow{t:P(\overline{n})} M, B, QP[t \mapsto QP(t)[\overline{n} \mapsto qp']] \xrightarrow{M, B, QP \xrightarrow{t:\varepsilon} M', B, QP[t \mapsto QP(t)[\overline{n} \mapsto qp]]}

with (M \triangleleft \alpha)(x) \triangleq \begin{cases} v & \text{if } \alpha = \beta \cdot (x := v) \cdot - \wedge \forall v'. \ x := v' \notin \beta \\ M(x) & \text{if } \forall v. \ x := v \notin \alpha \end{cases}

qp' = qp[req_L \mapsto \alpha][in_R \mapsto (x := \overline{y}) \cdot qp.in_R]

M' = M

qp.req_L = \alpha \cdot (x = \overline{y})

qp' = qp[in_R \mapsto \alpha][out_R \mapsto (x := \overline{y}) \cdot qp.out_R]

M' = M

\vee qp.in<sub>R</sub> = \alpha \cdot (x := \overline{y})

\operatorname{qp.wb}_{\mathbf{R}} = \varepsilon \operatorname{qp'} = \operatorname{qp}[\operatorname{out}_{\mathbf{R}} \mapsto \alpha \cdot (x := M(\overline{y})) \cdot \beta] M' = M

\vee qp.out<sub>R</sub> = \alpha \cdot (x := \overline{y}) \cdot \beta

\vee \text{ qp.out}_{\mathbf{R}} = \alpha \cdot (x := v)

qp' = qp[out_R \mapsto \alpha][rsp_L \mapsto (x:=v) \cdot qp.rsp_L]

M' = M

\vee \text{ qp.rsp}_{L} = \alpha \cdot (x := v)

qp' = qp[rsp_L \mapsto \alpha][wb_L \mapsto cn \cdot (x:=v) \cdot qp.wb_L]

M' = M

\mathsf{M}' = \mathsf{M}[x \mapsto v]

\vee \operatorname{qp.wb_{L}} = \alpha \cdot (x := v) \cdot \operatorname{cn}^{*}

qp' = qp[\mathbf{w}\mathbf{b}_L \mapsto \alpha \cdot \mathsf{cn}^*]

M, qp \rightarrow_{qp} M', qp'

qp' = qp[req_L \mapsto \alpha][in_R \mapsto (\overline{y} := M(x)) \cdot qp.in_R]

qp.req_L = \alpha \cdot (\overline{y} := x)

qp.\mathbf{w}\mathbf{b}_{L} = cn^{*}

M' = M

\vee \text{ qp.in}_{\mathbf{R}} = \alpha \cdot (\overline{y} := v)

qp' = qp[in_R \mapsto \alpha][wb_R \mapsto (\overline{y}:=v) \cdot qp.wb_R][out_R \mapsto ack_p \cdot qp.out_R] M' = M

\vee \text{ qp.}\mathbf{wb_R} = \alpha \cdot (\overline{y} := v)

M'=M[\overline{y}\mapsto v]

qp' = qp[wb_R \mapsto \alpha]

qp' = qp[out_R \mapsto \alpha][rsp_L \mapsto ack_p \cdot qp.rsp_L]

M' = M

\vee qp.out<sub>R</sub> = \alpha \cdot ack_p

M' = M

\vee qp.rsp<sub>L</sub> = \alpha \cdot ack_p

qp' = qp[rsp_L \mapsto \alpha][wb_L \mapsto cn \cdot qp.wb_L]

M, qp \rightarrow_{qp} M', qp'

qp.in_R = qp.out_R = qp.rsp_L = \varepsilon qp' = qp[req_L \mapsto \alpha]

qp.req_L = \alpha \cdot (rfence \overline{n})

M, qp \rightarrow_{qp} M, qp'

```

Fig. 7. RDMATSO hardware domains (above), hardware transitions (middle) and queue-pair transitions (below)

premise, with each disjunct corresponding to a step in  $G_1$ – $G_6$ . That is, if any of the six disjuncts in the premise of the rule hold, then the transition is enabled. Analogously, the second  $\rightarrow_{qp}$  transition describes how a put operation proceeds through the queue-pair pipeline, with each of the five disjuncts describing one of the five steps in  $P_1$ – $P_5$  (p. 11). Finally, the last  $\rightarrow_{qp}$  transition describes

$$\frac{P \xrightarrow{t:\epsilon} P'}{P, M, B, QP \Rightarrow P', M, B, QP} \qquad \frac{M, B, QP \xrightarrow{t:\epsilon} M', B', QP'}{P, M, B, QP \Rightarrow P, M', B', QP'} \qquad \frac{P \xrightarrow{t:l} P' \quad M, B, QP \xrightarrow{t:l} M', B', QP'}{P, M, B, QP \Rightarrow P', M', B', QP'}$$

Fig. 8. RDMA<sup>TSO</sup> operational semantics with the program and hardware transitions given in Fig. 6 and Fig. 7

the execution of a remote fence as described in §3.1, ensuring that it can only proceed if there are no pending operations on the queue pair (i.e.  $qp.in_R = qp.out_R = qp.rsp_L = \varepsilon$ ).

**RDMA**<sup>TSO</sup> **Combined Transitions**. The RDMA<sup>TSO</sup> operational semantics is defined by combining its program and hardware transitions as shown in Fig. 8. When the program subsystem takes a silent step, then the hardware subsystem is unchanged (first transition); analogously, when the hardware subsystem takes a silent step, then the program subsystem is unchanged (second transition). Finally, when the program and hardware subsystems both take the same transition (with the same label and by the same thread), then the transition effect is that of their combined effects.

Operational Semantics without PCIe. Recall from §2 (p. 8) that we model the PCIe-specific guarantee where a NIC remote read propagates all pending NIC remote writes (in  $\mathbf{wb_R}$ ) to memory, while a NIC local read propagates all pending NIC local writes (in  $\mathbf{wb_L}$ ) to memory. Nevertheless, we can relax this as follows. For NIC remote reads, we can replace the highlighted premises of the get queue-pair transition (top  $\rightarrow_{qp}$  transition) in Fig. 7 with  $qp' = qp[\mathbf{out_R} \mapsto \alpha \cdot (x := (M \lhd \mathbf{wb_R})(\overline{y})) \cdot \beta]$ . That is, we no longer require  $\mathbf{wb_R}$  to be empty (i.e. there may be pending writes in  $\mathbf{wb_R}$ ), and when reading the value of  $\overline{y}$  we first check for pending writes on  $\overline{y}$  in  $\mathbf{wb_R}$ .

For NIC local reads, we can similarly replace the highlighted premises of the put queue-pair transition (middle  $\rightarrow_{qp}$  transition) with  $qp' = qp[req_L \mapsto \alpha][in_R \mapsto (\overline{y} := (M \triangleleft wb_L)(x)) \cdot qp.in_R]$ . That is, we no longer require  $wb_L$  to contain only completion notifications (and allow it also to contain pending writes), and we first check  $wb_L$  for pending writes when reading the value of x.

**Observations**. Given a thread t and its store buffer b, all remote operations by t also go through b. Hence, as store buffers are FIFO, a CPU write cc in b before a remote operation rc in b always reaches the memory before rc is debuffered, and thus cc is visible to rc. Moreover, as all six buffers of the queue-pair pipeline are FIFO, remote operations maintain the order in which they were issued as they go through the queue-pair pipeline. Therefore, a thread always receives the completion notifications of get/put operations in the order they were submitted (i.e. the program order).

Observe that an rFence stipulates that only  $in_R$ ,  $out_R$  and  $rsp_L$  be empty but not  $wb_L$  and  $wb_R$ . As such, rFence cannot guarantee that the result of earlier put (resp. get) operations have reached the remote (resp. local) memory: they can still be pending in  $wb_R$  (resp.  $wb_L$ ). Moreover, rFence has no bearing on CPU operations and does not block their execution. Hence, later CPU operations (after rFence) may be visible to earlier get/put operations (those before rFence).

Recall that a put operation  $x^n := y$  comprises a local read from y and a remote write to x, and a get operation  $x := y^n$  comprises a remote read from y and a local write to x. Note that the local read of a put is fulfilled when it reaches the head of  $\operatorname{in}_R$  and is subsequently forwarded to  $\operatorname{out}_R$ . This ensures that puts are executed in program order and that puts are executed before all later gets (as in Fig. 2g). By contrast, the remote read of a get is fulfilled while in  $\operatorname{out}_R$  non-deterministically (i.e. not necessarily when it is at the head of  $\operatorname{out}_R$ ). This means that remote reads of gets can be reordered with respect to one another, as well as with respect to the remote writes of puts (as in Fig. 2h). Such reorderings can be prevented by adding an referee after a get (as in Fig. 2i).

Lastly, note that a poll retrieves the earliest cn in  $\mathbf{wb_L}$  (i.e. at its head). In the case of gets, the result of the get (its local write) is sent to  $\mathbf{wb_L}$  before its associated cn. As such, if the head of  $\mathbf{wb_L}$  is cn, then its result is guaranteed to have reached the memory of the local node when polling. By contrast, in the case of puts, its remote write operation could still be in  $\mathbf{wb_R}$  when polling, and thus polling a put cannot guarantee that the effect of the put has reached the remote memory.

# 3.3 RDMA<sup>TSO</sup> Simplified Operational Semantics

The concrete operational semantics in §3.2 reflects the structure of the underlying hardware, namely that of the six buffers in a queue pair. However, since all four buffers ( $\mathbf{req_L}$ ,  $\mathbf{in_R}$ ,  $\mathbf{out_R}$ ,  $\mathbf{rsp_L}$ ) in the middle are FIFO, we can simplify them by modelling them as a  $\mathit{single}$  buffer. Specifically, we model a  $\mathit{simple}$  queue  $\mathit{pair}$ ,  $\mathit{sqp} \in \mathsf{SQPair}^{\overline{n}}_n \triangleq \mathsf{Pipe}^{\overline{n}}_n \times \mathsf{WBR}^{\overline{n}}_n \times \mathsf{WBL}^{\overline{n}}_n$ , as a tuple comprising a  $\mathit{pipe}$ , as well as local and remote write-back buffers (as before). A  $\mathsf{pipe}$ ,  $\mathsf{pipe} \in \mathsf{Pipe}^{\overline{n}}_n \triangleq \{y^{\overline{n}} := x^n, y^{\overline{n}} := v, \mathsf{ack_p}, x^n := y^{\overline{n}}, x^n := v, \mathsf{rfence} \ \overline{n}\}^*$ , is simply a sequence of puts, gets, simplified puts and gets (with values), acknowledgements, and remote fences.

The program and command transitions of our simplified semantics is identical to those of the concrete one (Fig. 6). Moreover, the hardware transitions of our simplified semantics are those of the concrete semantics (Fig. 7), except that the queue-pair transitions at the bottom of Fig. 7 are replaced with the *simplified queue-pair transitions* given in §B. As before, the simplified operational semantics is obtained by combining its program and hardware transitions (Fig. 8).

Finally, we show that our concrete operational semantics is equivalent to the simplified one. We have mechanised our proof in Coq, available in the supplementary material [Ambal et al. 2024], with an overview of the proof available in §B.

THEOREM 3.1. The concrete RDMA<sup>TSO</sup> operational semantics is equivalent to the simplified one.

# 4 RDMA<sup>TSO</sup> Declarative Semantics

**Events and Executions**. In the literature of declarative models, the traces of a program are commonly represented as a set of *executions*, where an execution is a graph comprising: i) a set of *events* (graph nodes); and ii) a number of relations on events (graph edges). Each event is associated with the execution of a primitive command (in PComm) and is a tuple  $(\iota, t, l)$ , where  $\iota$  is the (unique) *event identifier*,  $t \in Tid$  identifies the executing thread, and  $l \in ELab$  is the *event label*, defined below.

Definition 4.1 (Labels and events). An event,  $e \in Event$ , is a triple  $(\iota, t, l)$ , where  $\iota \in \mathbb{N}$ ,  $t \in Tid$  and  $l \in ELab_{n(t)}$ . The set of event labels is  $ELab \triangleq \bigcup_n ELab_n$  for all nodes n. An event label of n,  $l \in ELab_n$ , is a tuple of one of the following forms:

- (CPU) local read:  $l = 1R(x^n, v_r)$

- (CPU) local write:  $l = 1W(x^n, v_w)$

- (CPU) CAS:  $l = CAS(x^n, v_r, v_w)$

- (CPU) memory fence: l = F

- (CPU) poll:  $l = P(\overline{n})$

- NIC local read:  $l = nlR(x^n, v_r, \overline{n})$

- NIC remote write:  $l = nrW(y^{\overline{n}}, v_w)$

- NIC remote read:  $l = nrR(y^{\overline{n}}, v_r)$

- NIC local write:  $l = n1W(x^n, v_w, \overline{n})$

- NIC fence:  $l = nF(\overline{n})$

Each event label denotes whether the associated primitive command is handled by the NIC (right column, prefixed with n), or the CPU (left column). A poll instruction is handled by the CPU (it simply awaits for a completion notification from the NIC). A put operation  $x^n := y$ , which consists of a NIC local read from y and a NIC remote write to x, is modelled as two events of type nlR (on y) and nrW (on x). Similarly, a get  $x := y^n$  is modelled as two events of type nrR (on y) and nlW (on x).

We write type (l), loc(l),  $v_r(l)$ ,  $v_w(l)$ , n(l) and  $\overline{n}(l)$  for the type (e.g. 1R), location, read value, write value, node and remote node of l, where applicable; e.g.  $loc(nlR(x^n, v_r, \overline{n})) = x^n$ ,  $n(nlR(x^n, v_r, \overline{n})) = n$

and  $\overline{n}(nlR(x^n, v_r, \overline{n})) = \overline{n}$ . We lift these functions to events as expected. We write  $\iota(e)$ ,  $\iota(e)$ ,  $\iota(e)$  to project the corresponding components of an event  $e = (\iota, \iota, \iota)$ .

**Issue and Observation Points**. In what follows we distinguish between when an instruction is *issued* and when it is *observed*. Intuitively, an instruction is issued when it is processed by the CPU or the NIC, and it is observed when its effect is propagated to the local or remote memory. As such, since writes (be they by the CPU or NIC) are the only instructions that have an observable effect on memory, the time points at which they are issued and observed may differ. A CPU write is issued when it is added to the store buffer and is observed when it is debuffered and propagated to memory. Similarly, the local (resp. remote) write of a get (resp. put) is issued when it is added to  $\mathbf{wb_L}$  (resp.  $\mathbf{wb_R}$ ), and observed when it is propagated to memory. By contrast, all other events are *instantaneous* in that *either* they do not have an observable effect on memory and thus their issue and observation points coincide, *or* their effect is written to memory *immediately*. In particular, CAS operations are instantaneous. Note that the observation point of any instruction either coincides with its issue point (instantaneous events) or it follows its issue point (write events).

**Notation**. Given a relation r and a set A, we write  $r^+$  for the transitive closure of r;  $r^{-1}$  for the inverse of r;  $r|_A$  for  $r \cap (A \times A)$ ; and [A] for the identity relation on A, i.e.  $\{(a,a) \mid a \in A\}$ . We write  $r_1$ ;  $r_2$  for the relational composition of  $r_1$  and  $r_2$ :  $\{(a,b) \mid \exists c.\ (a,c) \in r_1 \land (c,b) \in r_2\}$ . When r is a strict partial order, we write  $r|_{\text{imm}}$  for the *immediate* edges in r, i.e.  $r \setminus (r;r)$ . Given a set of events E and a location x, we write  $E_x$  for  $\{e \in E \mid loc(e) = x\}$ . Given a set of events E and a label type  $E_x$ , we write  $E_x$  for  $\{e \in E \mid type(e) = X\}$ , and define its sets of  $E_x$  as  $E_x$ . The  $E_x$  is a  $E_x$  and  $E_x$  and  $E_x$  in  $E_x$  and  $E_x$  in  $E_x$  in  $E_x$  and  $E_x$  in  $E_x$  in  $E_x$  and  $E_x$  in  $E_x$  in

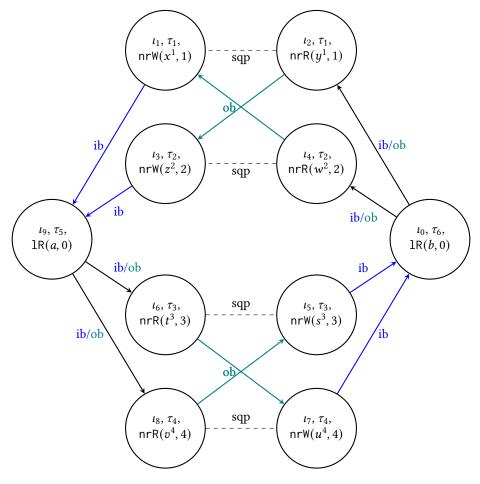

The 'same-location' relation is  $\operatorname{sloc} \triangleq \{(e, e') \in \operatorname{Event}^2 \mid \operatorname{loc}(e) = \operatorname{loc}(e')\}$ ; the 'same-thread' relation is  $\operatorname{sthd} \triangleq \{(e, e') \in \operatorname{Event}^2 \mid t(e) = t(e')\}$ ; and the 'same-queue-pair' relation is  $\operatorname{sqp} \triangleq \{(e, e') \in \operatorname{Event}^2 \mid t(e) = t(e') \land \overline{n}(e) = \overline{n}(e')\}$ . Note that  $\operatorname{sqp} \subseteq \operatorname{sthd}$  and that  $\operatorname{sloc}$ ,  $\operatorname{sthd}$  and  $\operatorname{sqp}$  are all symmetric. For a set of events E, we write E.sloc for  $\operatorname{sloc}|_{E}$ ; similarly for E.sthd and E.sqp.

*Definition 4.2 (Pre-executions).* A pre-execution is a tuple  $G = \langle E, po, rf, mo, pf, nfo \rangle$ , where:

- $E \subseteq$  Event is the set of events and includes a set of *initialisation* events,  $E^0 \subseteq E$ , comprising a single write with label  $\mathbb{IW}(x, 0)$  for each  $x \in \mathsf{Loc}$ .